fpga实操训练(从模块到系统开发)

source link: https://blog.csdn.net/feixiaoxing/article/details/128513160

Go to the source link to view the article. You can view the picture content, updated content and better typesetting reading experience. If the link is broken, please click the button below to view the snapshot at that time.

【 声明:版权所有,欢迎转载,请勿用于商业用途。 联系信箱:feixiaoxing @163.com】

前面我们学习了fpga的一些基本操作,熟悉了这些操作,基本上说fpga已经入门了。但是距离我们用fpga开发产品,这中间还有一些距离。这就好比,掌握了c语言的语法后,还不能立马来开发软件,还需要掌握数据库编程、qt编程、网络编程、多线程编程、文件读写、内存分配等等,如果涉及到业务层面,还有必要了解客户的作业流程,这样才能开发出符合客户需要的软件。fpga的学习过程也是一样,掌握了led、key、uart、数码管、pwm,以及熟悉了fpga rom、ram、fifo、lpm_mult、signal tap配置,加上状态机设计,这些都只是为后面的系统开发打下了基础。在这些工作的基础之上,还需要进一步的学习协议、算法和流程。个人建议,不妨从这几个地方入手,

1、掌握好通用的协议

目前通用的协议主要就是uart、spi、iic。外接的芯片、模块,一般都是根据这几个协议开发的。就拿spi来说,常用的就有flash、sd、时钟芯片、ad、da芯片。iic也很多,比如camera、eeprom、lcd屏等等。uart的话,调试、模块通信都有涉及。

也许有同学会说,需不需要学习ddr sdram。个人的体会,如果是ddr2,那么可以自己编写试试,从某金、某原子、某火那里学习fpga操作ddr2的方法,这是完全可以的。但是如果是ddr3、ddr4,自己只是拿来用,那么基本掌握好接口就可以了。因为对于很多fpga来说,比如xilinx,上面的ddr4、ddr3完全就是用Vivado MIG(memory interface generator)生成的,并不需要自己写verilog代码。

上面这些协议只是基础,本身并不复杂,大家不要有畏难情绪。一遍不行,那就两遍;两遍不行,那就三遍,总能学会的。以spi为例,它的信号一般就4个,分别是cs、clk、din、dout。cs是片选,clk是时钟,din是数据输入,dout是数据输出。四个信号里面,最重要的又是clk,

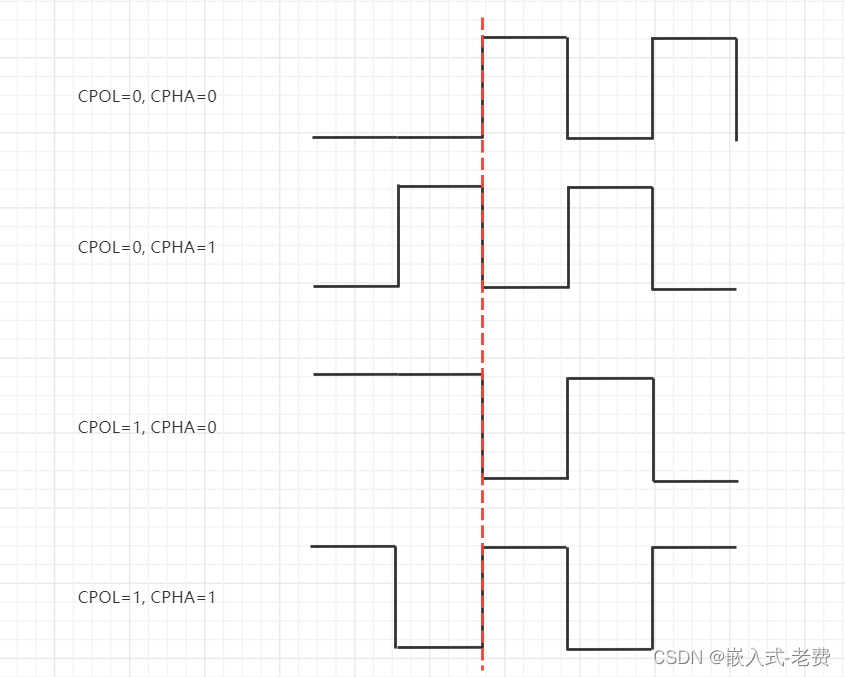

CPOL主要是描述空闲状态,clk信号是低电平,还是高电平。CPHA则表示,采样数据发生在第一个时钟跳变的时刻,还是第二个时钟跳变的时刻。所谓采样数据,表示的是接收数据的一方什么时候拿到这个数据。因此,作为数据的发送方来说,那就只能在采样的下一个时钟跳变的时候切换数据了。

2、学会读芯片手册(算法设计过程也类似)

协议和芯片的关系,有点类似于arm和soc的关系。不同厂家用arm做出来的soc是完全不一样的。而fpga要想实现自己的功能,就有必要和其他的芯片进行通信、交互。那怎么通信、频率多少、数据协议是什么,这就要求我们学会看芯片手册了。对于厂家来说,它的芯片会被用在很多的场合,厂家自己也不知道这个芯片会和谁连接,所以它只能把机械封装、引脚、电气、协议、最大频率、信号约束这些信息原原本本告诉开发者,这也是开发者debug的重要参考依据。以M25P16这颗16Mbit的spi norflash来说,它的官方文档就提供了大量的有效信息,我们挑几个做说明,

这段内容告诉我们这些信息,1)芯片16M bit;2)每一页有256 byte,一般1.4ms写一页,3)支持sector擦除,一个sector512k bit;4)支持16M bit擦除;5)支持2.7v到3.6v的电压输入;6)兼容SPI接口;7)最大时钟50M;8)支持深度省电模式,只需要1uA;9)支持电子签名;10)每个sector支持超过10万次擦除、编程;11)数据保存超过20年。

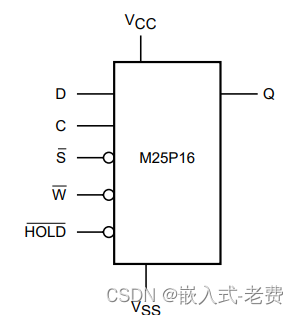

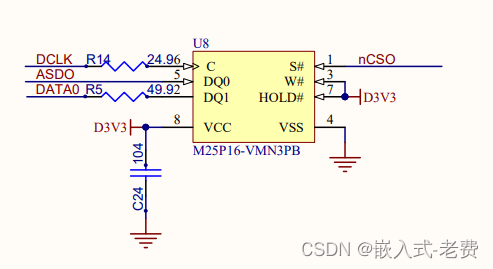

芯片逻辑图如上所示,VCC是电压+,Vss是地,D是数据输入,Q是数据输出,C是时钟,S是片选,W是写保护,HOLD是保持信号。

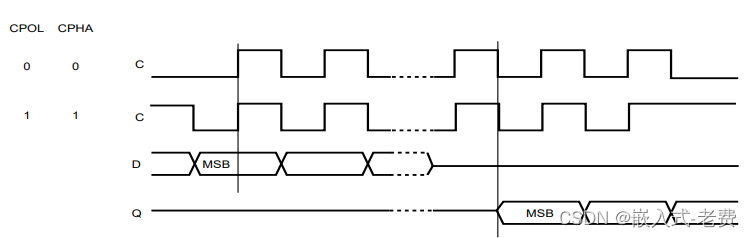

上面这张图表明芯片完全兼容SPI,支持CPOL=0,CPHA=0和CPOL=1,CPHA=1这两种模式。通常CPOL=0,CPHA=0写起来简单一些,可以写好spi之后,就可以做一些基本动作了。

表格中表示了芯片支持的命令,从上到下是写使能、写关闭、读取ID、读取状态寄存器、写状态寄存器、读取数据、快速读取数据、页编程、sector擦除、芯片擦除、深度省电、省电恢复,总共12条命令。因为flash只能从1写到0,如果从0写到1的话,就需要对sector或者整个芯片erase,这是需要注意的地方。

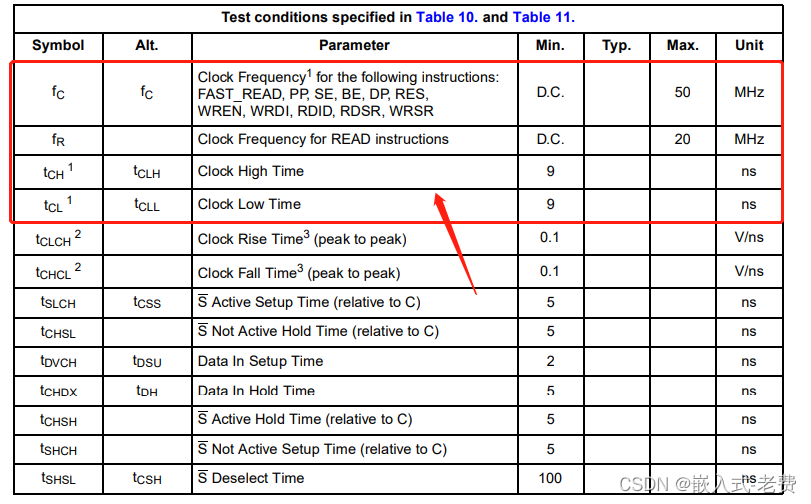

除了命令和协议之外,另外一个重要的就是时序。红框中就是这颗芯片比较重要的几个时序部分,读数据命令之外的其他命令最大不能超过50M,读数据命令不能超过20M,clock为high的时间不能低于9ns,clock为low的时间不能低于9ns。从clock的这个时间限制也说明了,频率不能超过1s/(9ns+9ns)=55M这个频率,和上面说的50M差不多。

一般来说,芯片之间的传输慢点没事,但是影响效率。关键是大家都想要快一点,但是不同芯片有自己的最大频率限制,这部分需要注意下。

3、查看和掌握电路原理图

学习了协议和芯片之后,最好再掌握一下原理图,也就是电路原理图。一来加深下印象;二来将来如果功能不正确,也知道元器件在哪,怎么去测试和度量。下面这幅图就是spi norflash的原理图,

4、编写代码做仿真

有了协议、芯片手册(或者算法)、电路图,下面要做的就是编写verilog代码。编写的过程中可能会反复查看协议和芯片手册,这都是常有的事情。写好代码后,一定要做仿真,仿真不仅速度快,而且可以提前发现很多的设计问题,这比fpga调试快多了。等到所有的仿真都解决了,再上板子测试,这是效率比较高的办法。fpga综合的速度慢,而且调试起来费时费力,远没有仿真这样方便和简洁。

5、运用signal tap、示波器和逻辑分析仪进行调试

不同的fpga可以选用不同的debug工具调试。这个大家可以根据自己选用的eda工具,灵活进行配置。仿真一般信号都是比较理想的,但是真实的硬件可能会出各种各样的情况,供电、排线插反、信号质量、频率、干扰、电源,方方面面都会有牵制。这个时候就要学会运用signal tap、示波器、逻辑分析仪等各种方法进行调试和验证了。

6、将自己的代码和第三方代码进行比较

平时阅读别人的代码的时候可能没什么感觉,可能认为功能就应该这么写。等到自己真正实践的时候,才会发现自己和别人的差距。在调试自己代码的时候,如果实在没有办法了,尝试去比较一下自己的代码以及别人的代码,寻找不同之处,往往会有很多意外的收获。也只有这样,才能让自己不断成长和进步。

Recommend

-

7

7

fpga实操训练(基础)

-

2

2

fpga实操训练(按键输入)

-

4

4

fpga实操训练(按键消抖)

-

5

5

fpga实操训练(锁相环pll)

-

5

5

fpga实操训练(数码管)

-

2

2

fpga实操训练(uart串口)

-

8

8

fpga实操训练(小功能到模块开发)

-

4

4

fpga实操训练(利用fpga实现pwm)

-

4

4

fpga实操训练(一个典型的fpga系统) ...

-

0

0

fpga实操训练(系统开发和硬件接口)

About Joyk

Aggregate valuable and interesting links.

Joyk means Joy of geeK

已于 2023-01-01 22:40:15 修改

已于 2023-01-01 22:40:15 修改

39

39