fpga实操训练(利用fpga实现pwm)

source link: https://blog.csdn.net/feixiaoxing/article/details/128392235

Go to the source link to view the article. You can view the picture content, updated content and better typesetting reading experience. If the link is broken, please click the button below to view the snapshot at that time.

【 声明:版权所有,欢迎转载,请勿用于商业用途。 联系信箱:feixiaoxing @163.com】

pwm,其实就是方波。它的本质就是通过方波中占空比的调节,实现对外部设备的控制。简单如台灯,复杂如电机都是这么做的。fpga输入的时钟信号是50M,每个时钟信号中高低电平的比率是50%对50%。那方波是什么样的呢?它的控制频率可能只有100,高低电平是的比率很有可能是10%对90%,那么这又该如何实现呢?

和之前的做法不同,今天我们首先给出verilog代码,再进一步分析。代码不长,主要的寄存器是start、stop和pwm。其中pwm是输出信号。

首先来看start信号,rst复位的时候被设置为0,随后开始每次自增8590。至于为什么每次增加这个数字,目前未知。

其次来看stop信号,rst复位的时候被设置位429_496_730,大约是4亿多。看样子没有越界。因为32位整数最大能表示的数值是40多亿。等rst被复位之后,这个数据就没有发生变化了。

最后来看pwm信号,这也是最重要的部分。因为pwm连接的是一个蜂鸣器,低电平有效,所以复位后默认输出是1。接着,在start小于stop这段时间内,蜂鸣器有效,发出声音;但是start大于stop的这段时间,蜂鸣器无效,停止发出声音。看到这里,很多同学都以为verilog分析完了,这就是一个开始发声、停止发声的verilog代码,和pwm没有关系。但是,请大家重新看下这段代码,

前面我们说过,32位数据表达的数值是有范围的。start不可能这样一直增加下去,等到了临界值之后,start又会重新小于stop,蜂鸣器又会发生,循环又开始了。这才是最终我们想要的效果。

分析完了之后,就是分析8590、429496730这些数字是怎么来的。首先假设输入的clk频率是50M,假设最终pwm的控制频率是100,则单次pwm内的时钟数应该是50000000/100=500000。

利用32位整数表达范围有限制的特定,对于2^32位整数来说,单次pwm里面的每一个clk相当于自增多少呢?那就是2^32/500000 = 8589.9,差不多就是8590,这正是start每次递增的数据。

而429496730代表什么呢?因为每次递增8589.9,差不多需要迭代500000次才能越界,而429496730/8589.9=50000左右,差不多占了500000次的10%所有,因此这个数据主要是调节单次pwm调节内的占空比的。实际的计算公式应该是,target = 500000*ratio*8589.9。

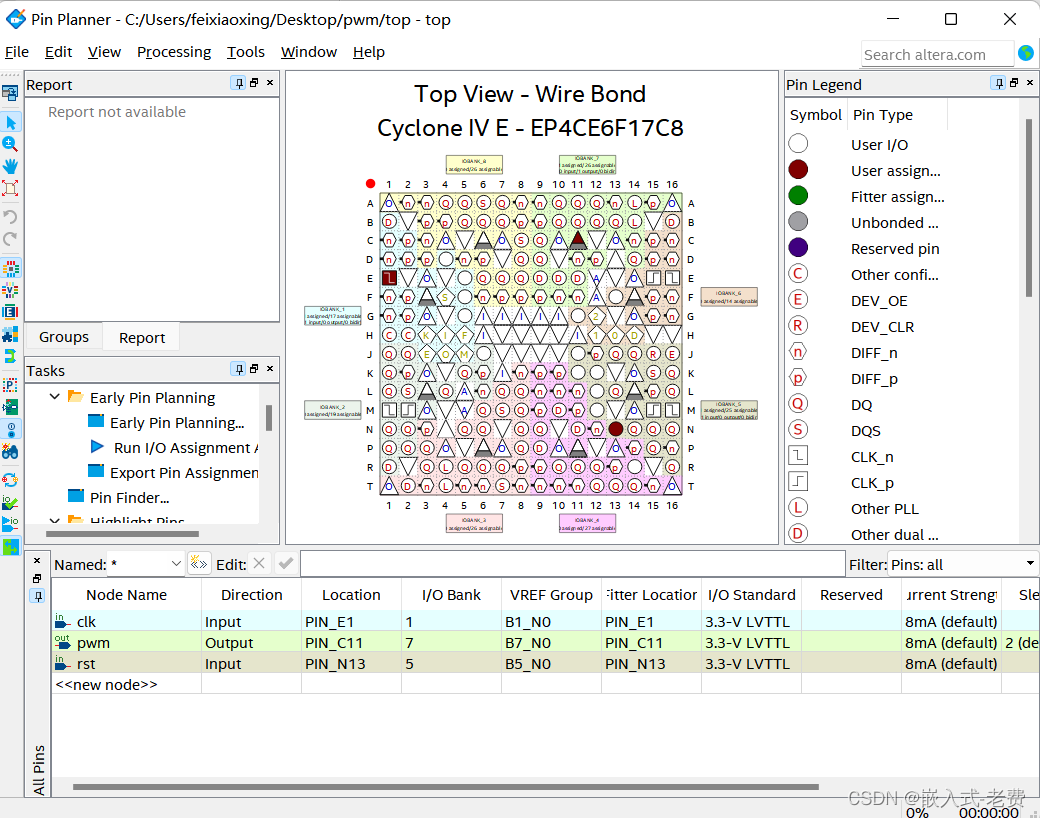

弄懂了原理之后,下面就是编译和pin绑定了。

实验的时候因为没有示波器,所以用了蜂鸣器做了实验。同样的频率内,ratio越大,蜂鸣器越响;反之则越闷,大家可以试试。

Recommend

About Joyk

Aggregate valuable and interesting links.

Joyk means Joy of geeK