台积电或2030年才采用High-NA EUV光刻机,用于制造1nm芯片

source link: https://www.expreview.com/92264.html

Go to the source link to view the article. You can view the picture content, updated content and better typesetting reading experience. If the link is broken, please click the button below to view the snapshot at that time.

台积电或2030年才采用High-NA EUV光刻机,用于制造1nm芯片

吕嘉俭发布于 2024-2-8 10:05

本文约 560 字,需 1 分钟阅读

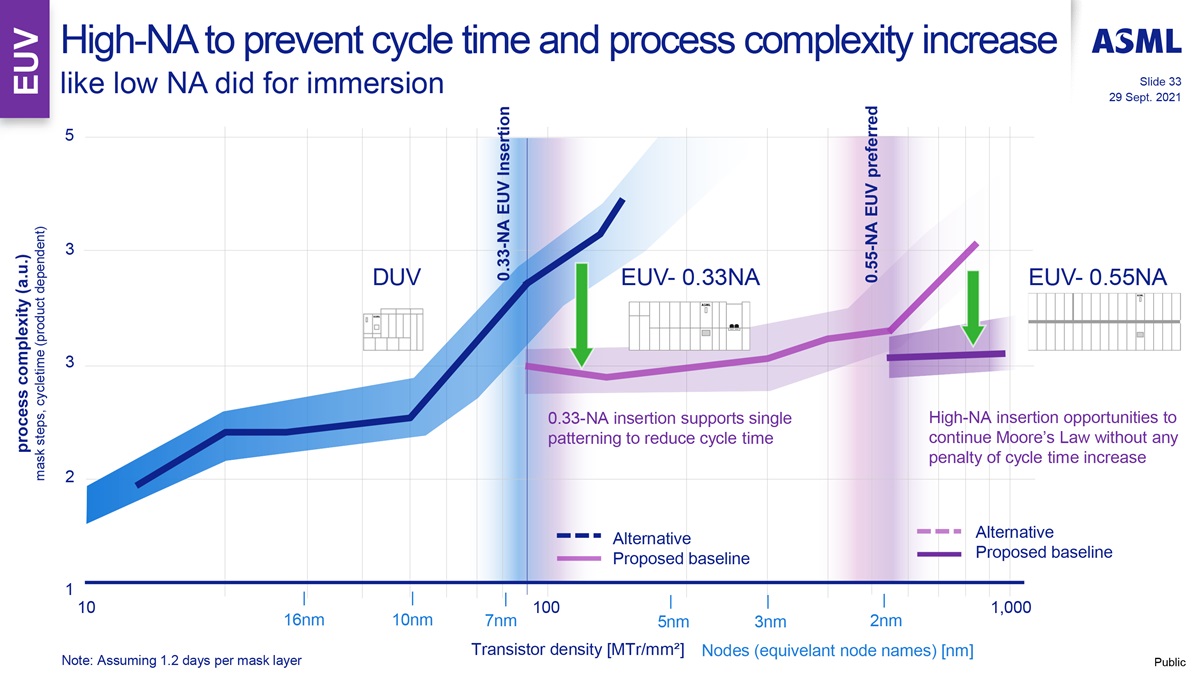

去年末,ASML向英特尔交付了业界首台High-NA EUV光刻机。这是具有高数值孔径(High-NA)和每小时生产超过200片晶圆的极紫外光(EUV)大批量生产系统,提供0.55数值孔径,与此前配备0.33数值孔径透镜的EUV系统相比,精度会有所提高,可以实现更高分辨率的图案化,以实现更小的晶体管特征。

英特尔打算在Intel 18A制程节点引入High-NA EUV光刻技术,这意味着大概在2026年至2027年之间开始启用新设备。事实上,台积电(TSMC)和三星都已表示会采购High-NA EUV光刻机,用于研发未来新的半导体工艺,不过没有设定任何的时间表。

据DigiTimes报道,来自于晶圆厂工具制造商的消息证实,台积电要等到1nm制程节点才会使用High-NA EUV光刻机,可能是出于对成本的考虑。根据台积电之前公布的路线图,1.4nm级A14工艺的推出时间大概在2027年至2028年之间,而1nm级A10工艺的开发预计会在2030年前完成。

此前ASML首次财务官Roger Dassen在接受采访时表示,High-NA EUV光刻机可以避免制造上双重或四重曝光带来的复杂性,在逻辑和存储芯片方面是最具成本效益的解决方案。显然并不是所有的芯片制造商都像英特尔那样急于将High-NA EUV光刻机用于芯片的量产,表面上可以降低总体成本,但毕竟现有的EUV光刻机也可以双重成像技术实现相同的效果。

由于计划会根据现有技术的表现以及其他市场因素而改变,所以台积电最后也可能会改变引入High-NA EUV光刻技术的时间点。

Recommend

About Joyk

Aggregate valuable and interesting links.

Joyk means Joy of geeK