Chiplet技术:既具备先进性,又续命摩尔定律

source link: https://server.51cto.com/article/759429.html

Go to the source link to view the article. You can view the picture content, updated content and better typesetting reading experience. If the link is broken, please click the button below to view the snapshot at that time.

Chiplet技术:既具备先进性,又续命摩尔定律

1、Chiplet 在成本、良率、设计灵活性等方面优势明显

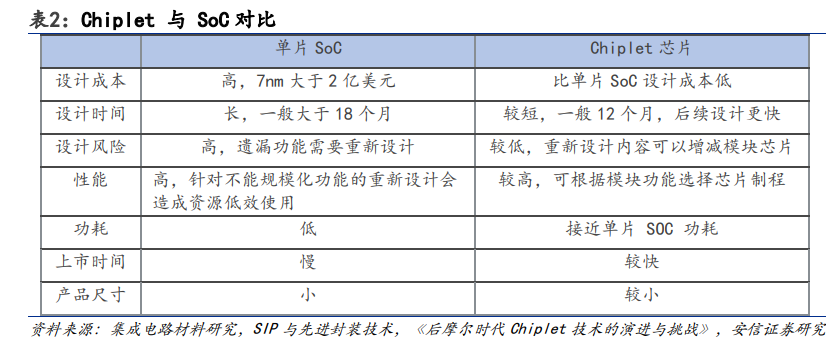

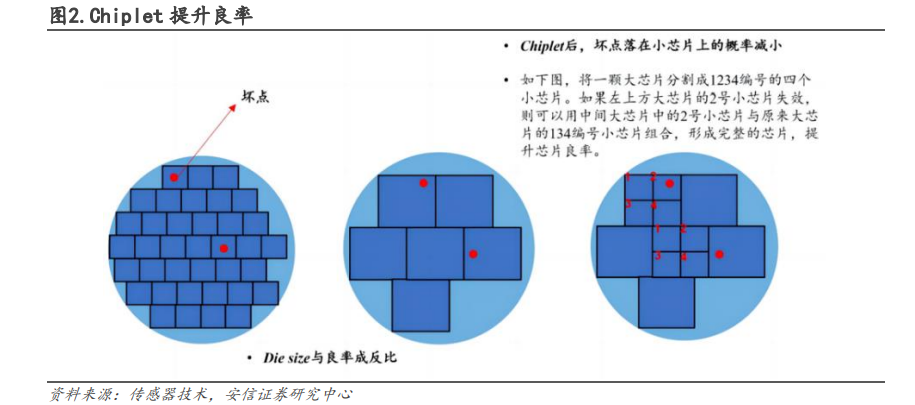

Chiplet 俗称“芯粒”或“小芯片组”,通过将原来集成于同一 SoC 中的各个元件分拆,独立 为多个具特定功能的 Chiplet,分开制造后再通过先进封装技术将彼此互联,最终集成封装 为一个系统芯片。

由于Chiplet芯粒可以独立设计和组装,因此制造商可以根据自己的需要来选择不同类型、不同规格和不同供应商的芯粒进 行组合,很大程度上提高了芯片设计的灵活性和可定制化程度;并且制造商可以依赖于预定 好的芯片工具箱来设计新产品,缩短芯片的上市时间。同时,Chiplet 技术可以将 大型 7nm 设计的成本降低高达 25%;在 5nm 及以下的情况下,节省的成本更大。

Chiplet 技术被视为“异构”技术的焦点,也是当下最被企业所认可的新型技术之一。2022 年 3 月,英特尔、AMD、Arm、高通、三星、台积电、日月光、Google Cloud、Meta、微软等 全球领先的芯片厂商共同成立了 UCIe 联盟,旨在建立统一的 die-to-die 互联标准,促进 Chiplet 模式的应用发展,目前联盟成员已有超过 80 家半导体企业,越来越多的企业开始研 发 Chiplet 相关产品。

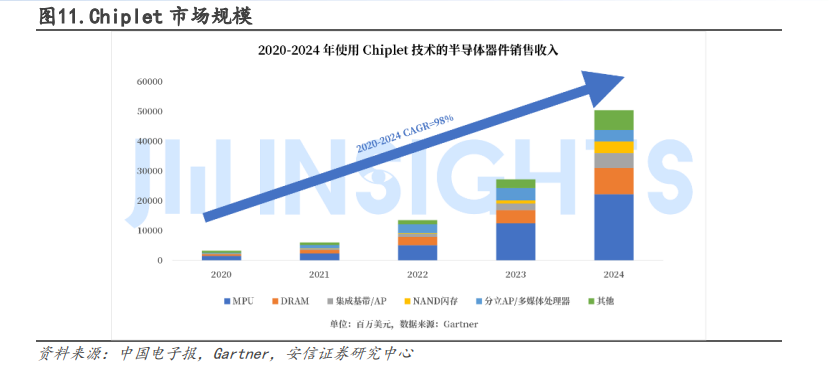

2、Chiplet市场规模快速成长

根据 Gartner 数据统计,基于 Chiplet 的半导体器件销售收入在 2020 年仅为 33 亿美元, 2022 年已超过 100 亿美元,预计 2023 年将超过 250 亿美元,2024 年将达到 505 亿美元,复 合年增长率高达 98%。超过 30%的 SiP 封装将使用芯粒(Chiplet)来优化成本、性能和上市 时间。

MPU 占据 Chiplet 大部分应用应用场景,Omdia 预测 2024 年用于 MPU 的 Chiplet 约占 Chiplet 总市场规模的 43%。

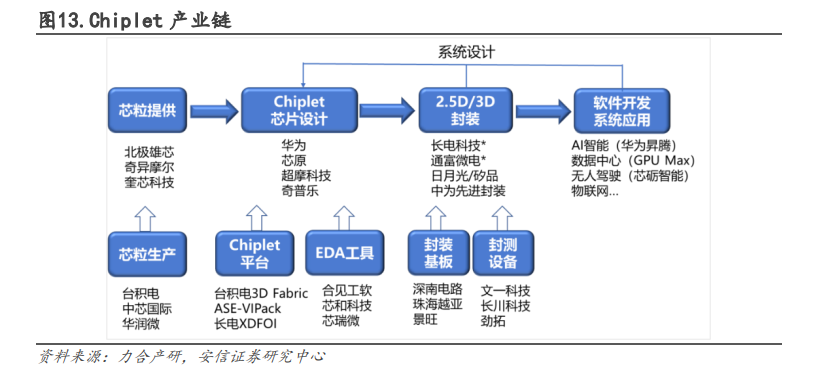

随着 Chiplet 技术的发展, Chiplet 产业链各环节逐渐完善,即由 Chiplet 系统级设计、EDA/IP、芯粒(核心、非核心、 IO Die、Base Die)、制造、封测组成的完整 Chiplet 生态链。

Chiplet 产业链主链有四大环节,包括芯粒、芯片设计、封装生产和系统应用,支撑环节包 括芯粒生产、设计平台、EDA 工具、封装基板、封测设备等领域。

3、IC 制造及封测厂加码布局 Chiplet

目前全球封装技术主要由台积电、三星、Intel 等公司主导,主要是 2.5D 和 3D 封装。2.5D 封装技术已非常成熟,广泛应用于 FPGA、CPU、GPU 等芯片,目前是 Chiplet 架构产品主要的 封装解决方案。3D 封装能够帮助实现 3D IC,即晶粒间的堆叠和高密度互连,可以提供更为 灵活的设计选择。但 3D 封装的技术难度更高,目前主要有英特尔和台积电掌握 3D 封装技术 并商用。台积电比三星、英特尔更早采用 Chiplet 的封装方式。

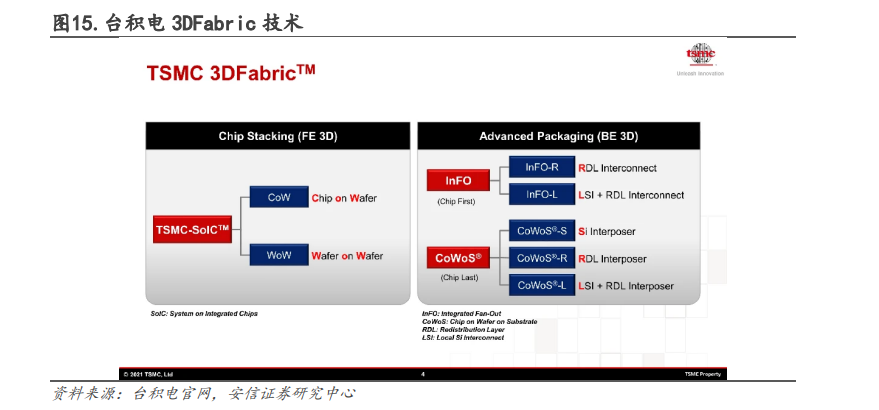

1)台积电3D Fabric封装技术

台积电推出了3D Fabric,搭载了完备的3D硅堆栈(3D Silicon Stacking)和先进的封装技术。3DFabric 是由台积电前端 3D 硅 堆栈技术 TSMC SoIC 系统整合的芯片,由基板晶圆上封装(Chip on Wafer on Substrate, CoWoS)与整合型扇出(Integrated Fan-Out, InFO)的后端 3D 导线连接技术所组成,能够 为客户提供整合异质小芯片(Chiplet)的弹性解决方案。该项技术先后被用于赛灵思的 FPGA、 英伟达的 GPU 以及 AMD 的 CPU。

2)Intel 2.5D 封装技术EMIB

Intel主导的 2.5D 封装技术为 EMIB,使用多个嵌入式包含多个路由层的桥接芯片,同时内 嵌至封装基板,达到高效和高密度的封装。由于不再使用 interposer 作为中间介质,可以去 掉原有连接至 interposer 所需要的 TSV,以及由于 interposer 尺寸所带来的封装尺寸的限制,可以获得更好的灵活性和更高的集成度。

相较于 MCM 和 CoWoS 技术,EMIB 技术获得更高 的集成度和制造良率。英特尔对各种先进封装产品组合 (如 Foveros、EMIB 和 Co-EMIB) 的 投资是实施公司新领导层所公布的 IDM2.0 战略的关键。

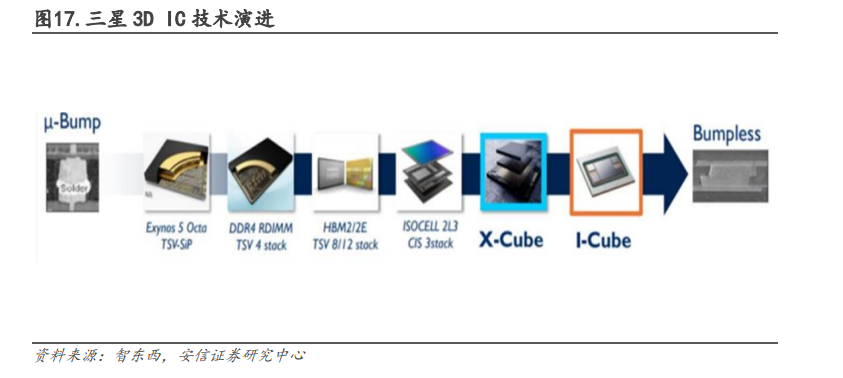

3)三星公X Cube 3D封装技术

三星也在积极投资先进的封装技术,以满足 HPC 应用在异质芯片整合的快速发展。2020 年 8 月,三星公布了 X Cube 3D 封装技术。在芯片互连方面,使用成熟的硅通孔 TSV 工艺。目前 X Cube 能把 SRAM 芯片堆叠在三星生产的 7nm EUV 工艺的逻辑芯片上,在更易于扩展 SRAM 容 量的同时也缩短了信号连接距离,提升了数据传输的速度。此后发布的 I-Cube 可以将一个 或多个逻辑Die 和多个 HBM die 水平放置在硅中介层,进行异构集成。

4)日月光FOCoS先进封装技术

日月光凭借在 FOCoS 先进封装技术的布局,是目前在封测代工厂中唯一拥有超高密度扇出解 决方案的供应商。日月光的 FOCoS 提供了一种用于实现小芯片集成的硅桥技术,称为 FOCoSB(桥),它利用带有路由层的微小硅片作为小芯片之间的封装内互连,例如图形计算芯片 (GPU)和高带宽内存(HBM)。硅桥嵌入在扇出 RDL 层中,是一种可以不使用硅中介层的 2.5D 封 装方案。与使用硅中介层的 2.5D 封装相比,FOCoS-B 的优势在于只需要将两个小芯片连接在 一起的区域使用硅片,可大幅降低成本。

5)长电科技2.5D TSV-less封装技术

长电科技推出的面向Chiplet小芯片的高密度多维异构集成技术平台 XDFOI可实现 TSV-less 技术,达到性能和成本的双重优势,重点应用领域为高性能运算如 FPGA、5G、自动驾驶、智能医疗等。XDFOI是一种以 2.5D TSV-less 为基本技术平台的封装技术, 在线宽/线距可达到 2μm/2μm 的同时,还可以实现多层布线层,以及 2D/2.5D 和 3D 多种异 构封装,能够提供小芯片(Chiplet)及异构封装的系统封装解决方案。目前长电先进 XDFOI 2.5D 试验线已建设完成,并进入稳定量产阶段,同步实现国际客户 4nm 节点多芯片系统集成 封装产品出货。

Recommend

About Joyk

Aggregate valuable and interesting links.

Joyk means Joy of geeK