台积电N3系列工艺无法提高SRAM密度,已经与逻辑密度提升没有关系

source link: http://www.expreview.com/88578.html

Go to the source link to view the article. You can view the picture content, updated content and better typesetting reading experience. If the link is broken, please click the button below to view the snapshot at that time.

台积电N3系列工艺无法提高SRAM密度,已经与逻辑密度提升没有关系

吕嘉俭发布于 2023-5-30 17:00

上个月,台积电(TSMC)介绍了先进半导体制造工艺的路线图,包括了3nm和2nm制程节点的各种工艺。今年台积电将推出改进的N3E工艺,成本更低,有着更好的经济效益,接下来会在3nm制程节点提供更广泛的产品组合,包括N3P、N3X和N3AE,以满足不同客户的多样化需求。

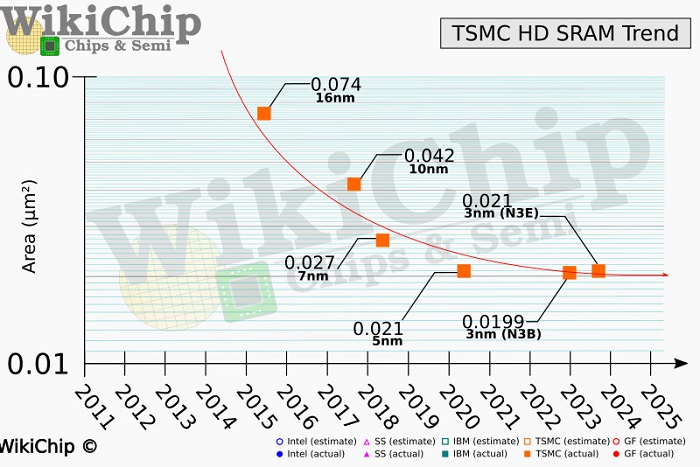

WikiChip表示,近期得到的信息显示,SRAM单元在台积电3nm制程节点上,与5nm制程节点基本没有分别。虽然台积电在早期曾表示,新的制程节点在SRAM单元的密度上是上一代工艺的1.2倍,不过根据最新的信息,差别非常小。此前就有报道称,台积电在3nm制程节点遇到SRAM单元缩减放缓的问题。

据了解,台积电在改进的N3E工艺上,引入了英特尔早在2011年22nm时期就采用的SAC方案,提高了良品率。不过无论N3E工艺如何改进,SRAM单元的密度都没多大差别。这也导致了今天台积电谈及新制程节点的进步时,主要还是说逻辑密度及制造步骤的改进,有意回避了这方面的问题。

现代处理器里,SRAM占据了芯片很大一部分面积和晶体管数量,如果没有明显改进,芯片换用新的制程节点效果就不太明显了。何况台积电的3nm制程节点成本大幅度飙升,导致了许多芯片公司都选择观望,没有去下单。事实上,SRAM缩减已经不再跟随逻辑密度提升,这样的情况已经有一段时间了,只是两者现在已经没有什么关联。

Recommend

About Joyk

Aggregate valuable and interesting links.

Joyk means Joy of geeK