手把手教你蜂鸟e203移植(以Nexys4DDR为例) - 敲好听的名字捏

source link: https://www.cnblogs.com/Qzzz/p/17201475.html

Go to the source link to view the article. You can view the picture content, updated content and better typesetting reading experience. If the link is broken, please click the button below to view the snapshot at that time.

手把手教你蜂鸟e203移植(以Nexys4DDR为例) - 敲好听的名字捏 - 博客园

准备工作:(网盘链接:)

1.蜂鸟e203的RTL源码;

2.一段分频代码;

3.顶层设计文件(system.v)

4.开发板文件;

5.Nexys4DDR电路图;

6.Nexys4DDR管脚约束模板;

7.Nexys4DDR官方文档。

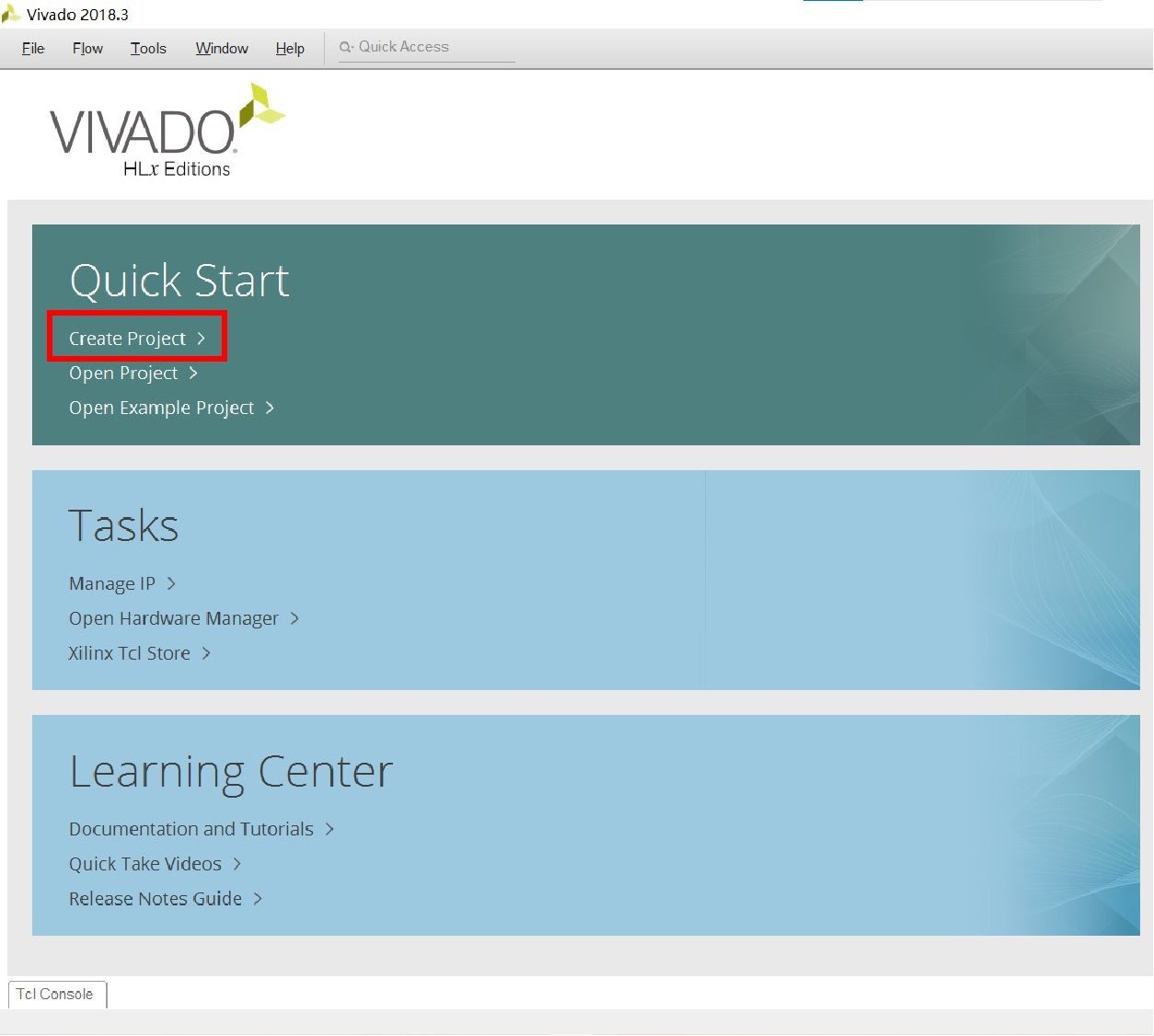

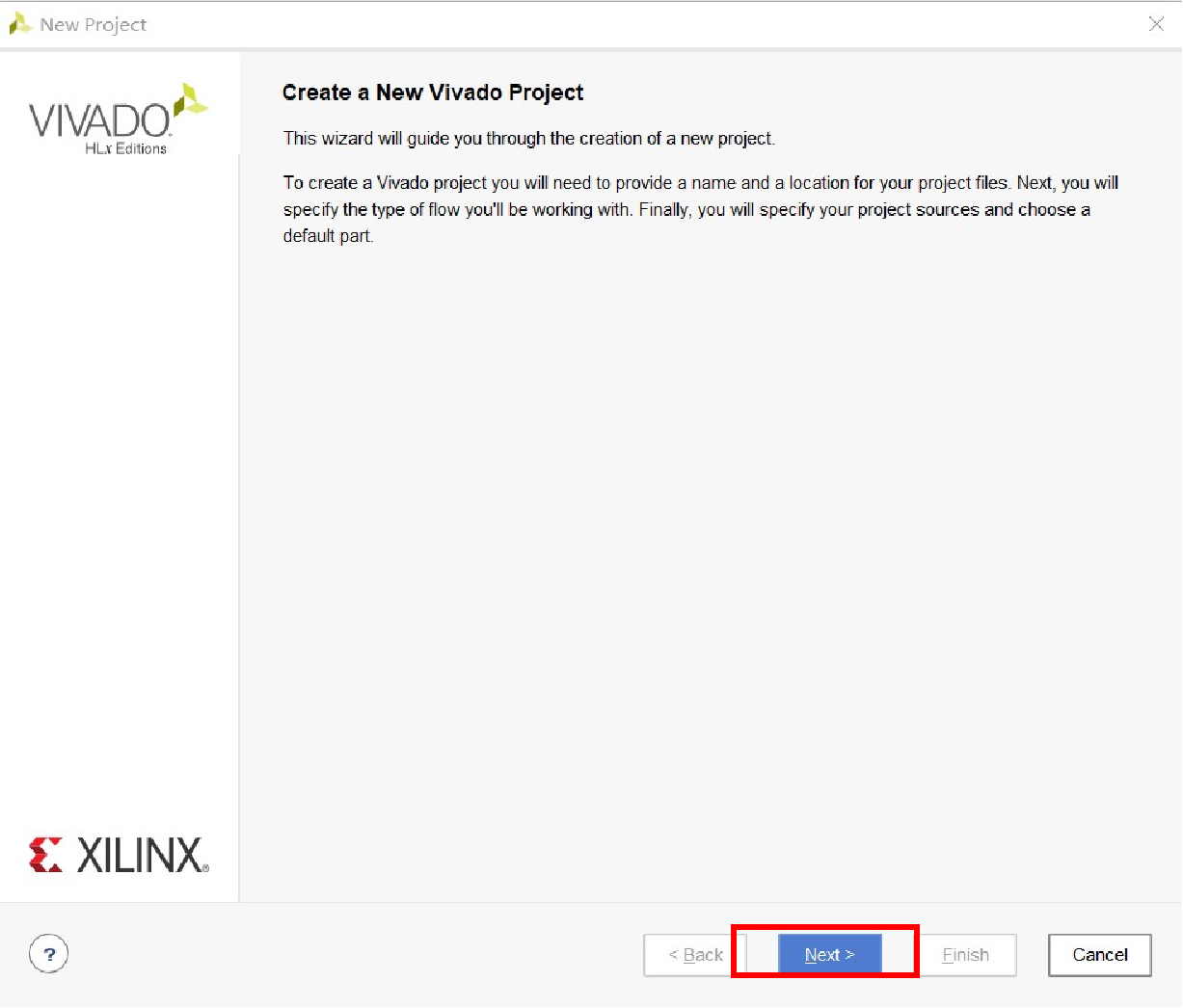

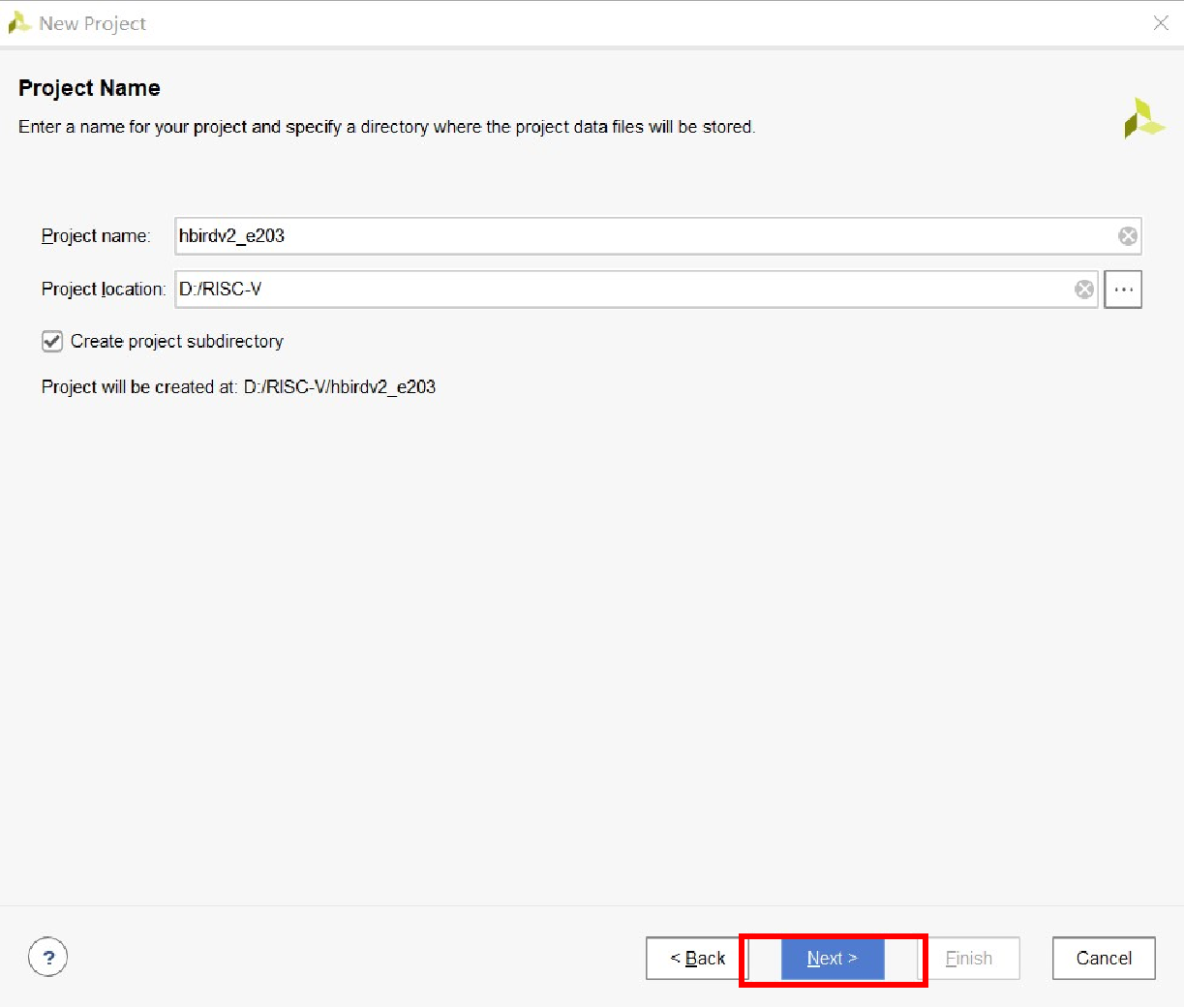

在Vivado中创建工程,命名随意,路径随意;

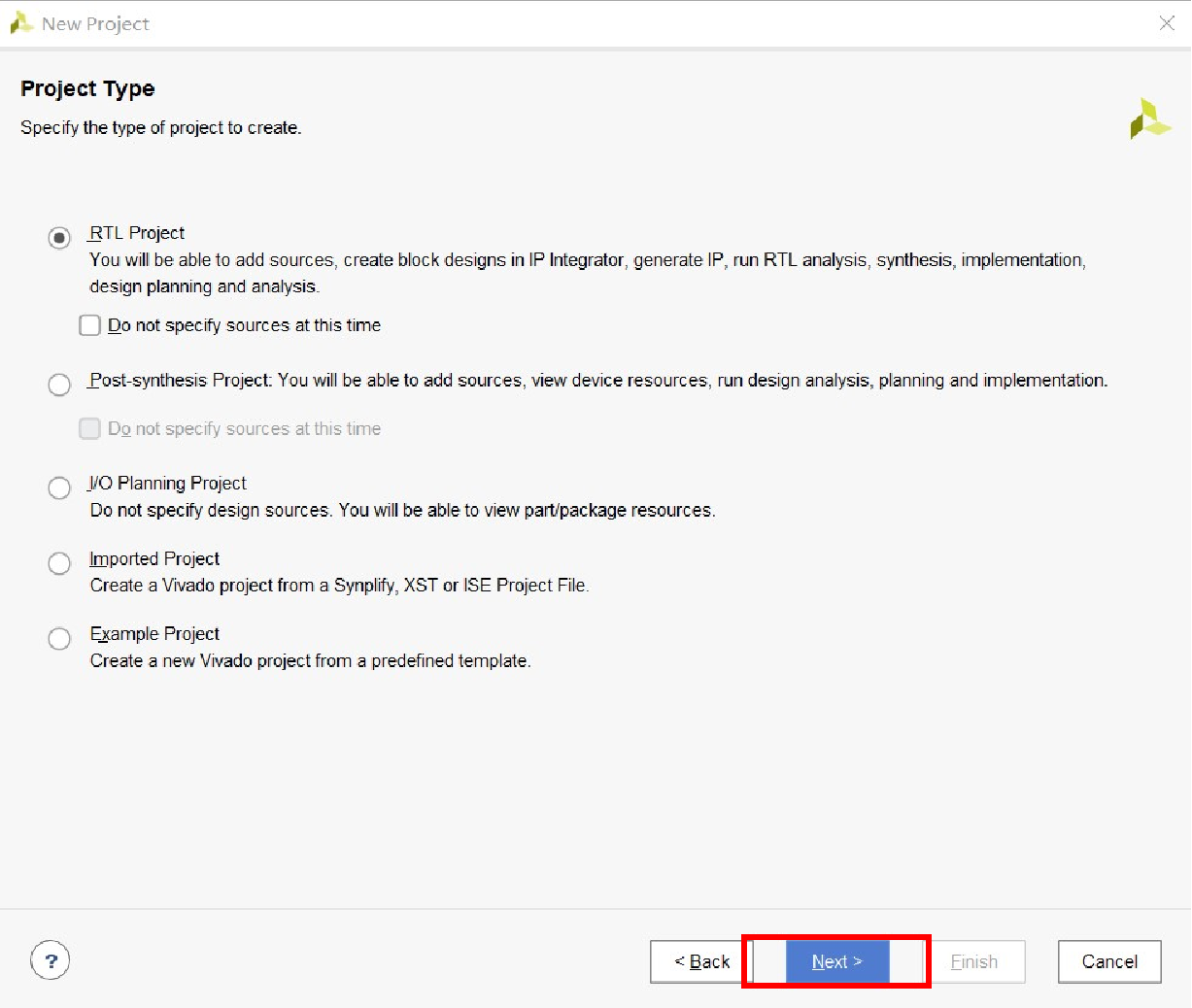

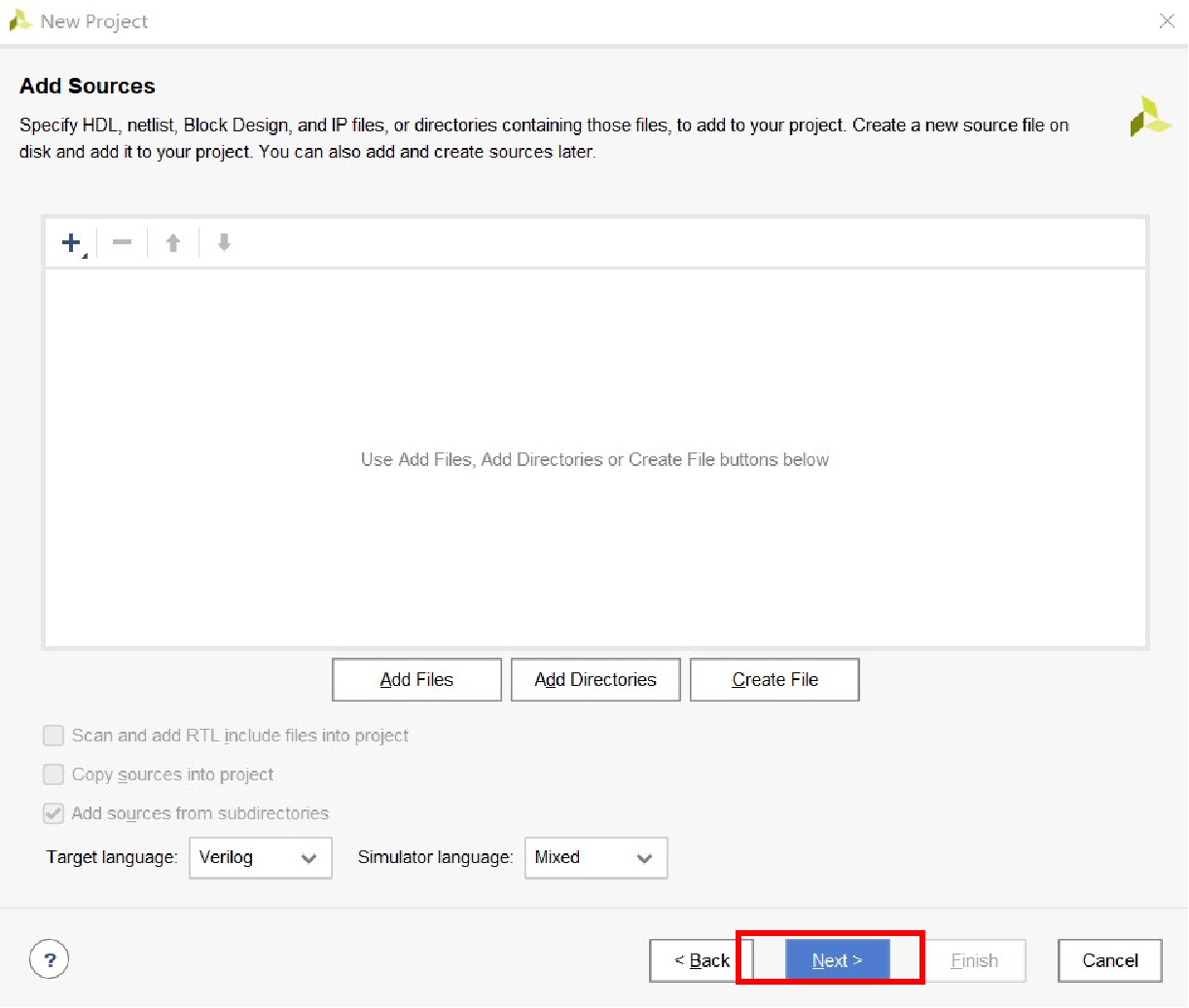

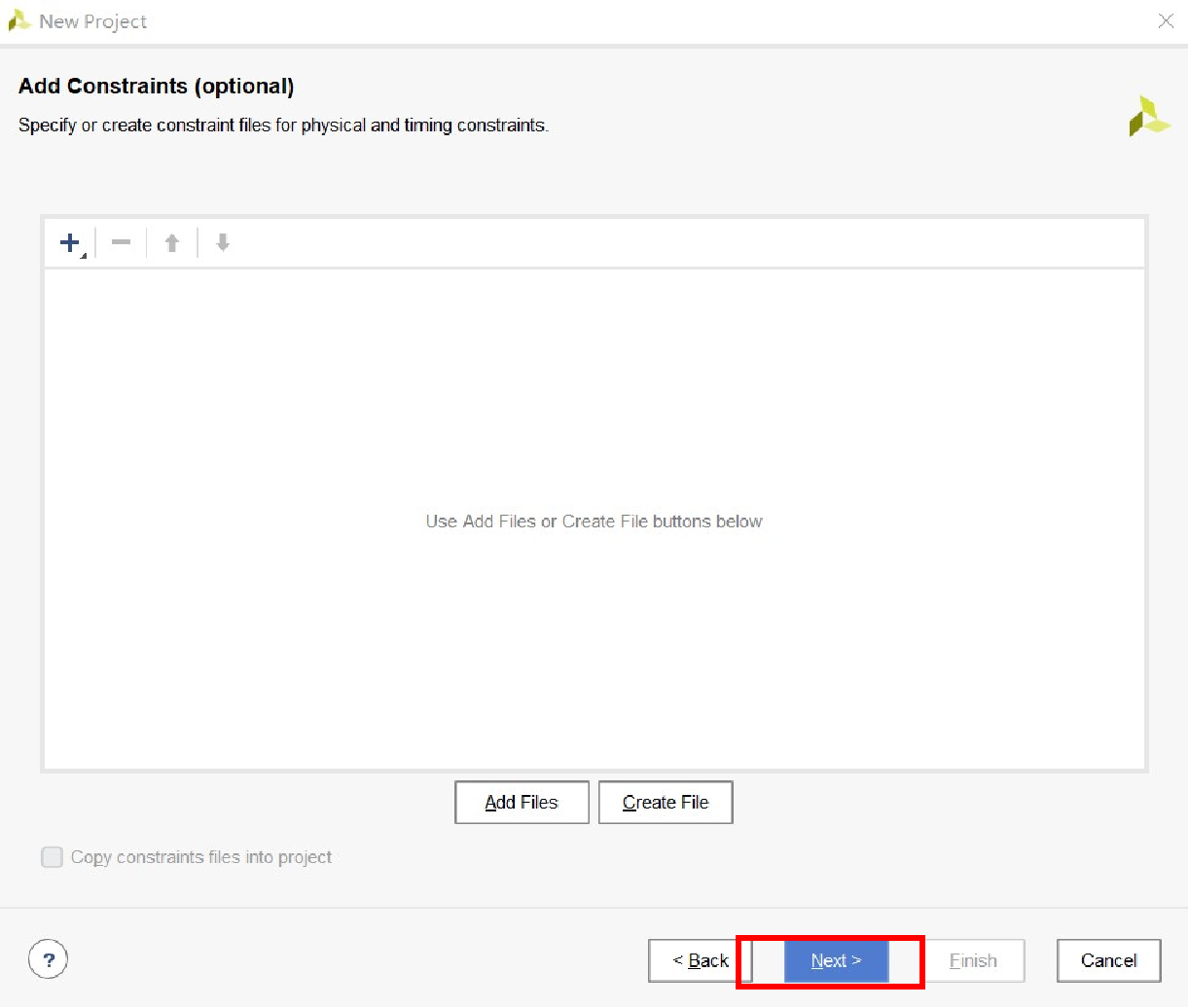

这里可以选择是否添加源文件等,我们先不添加;

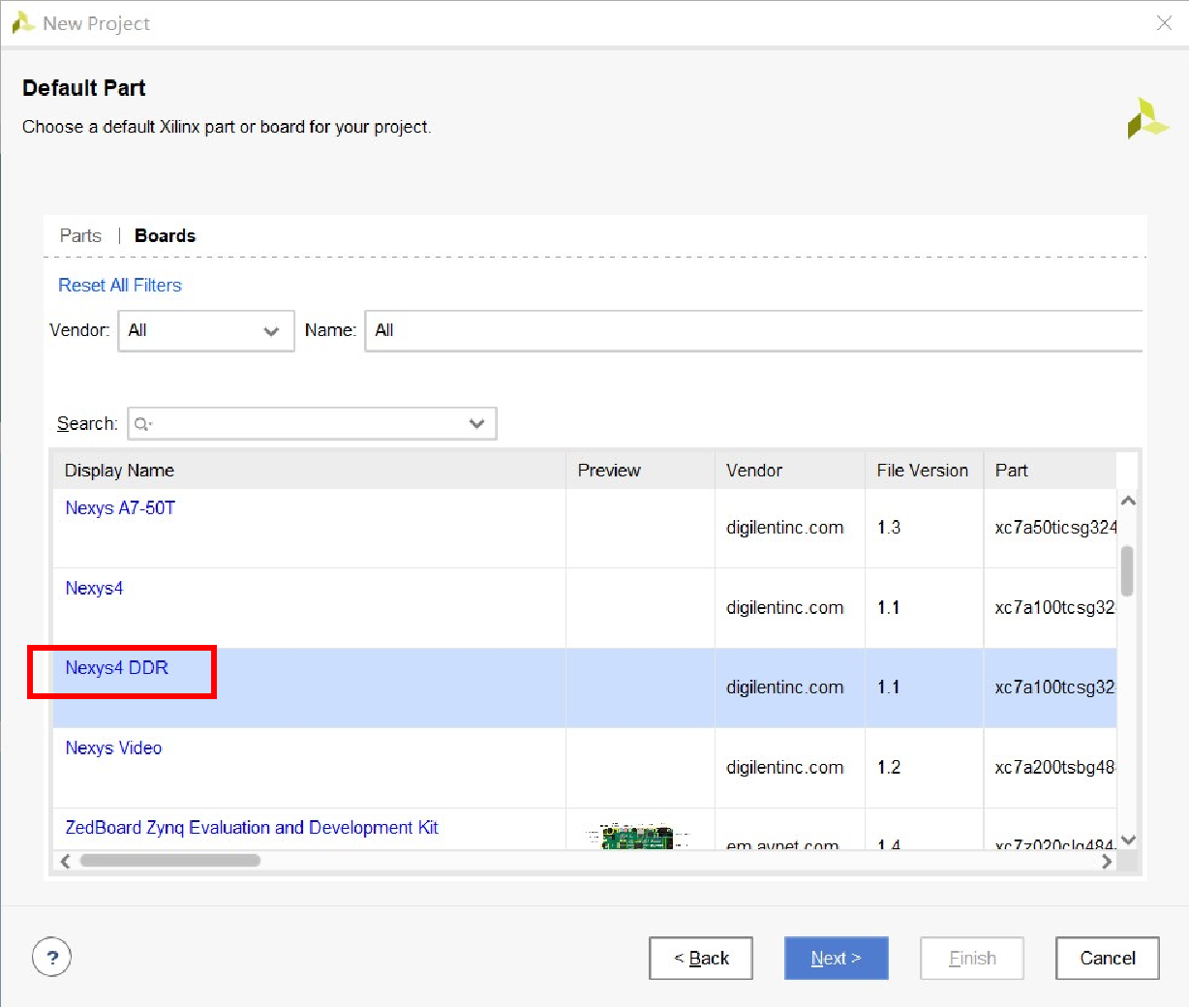

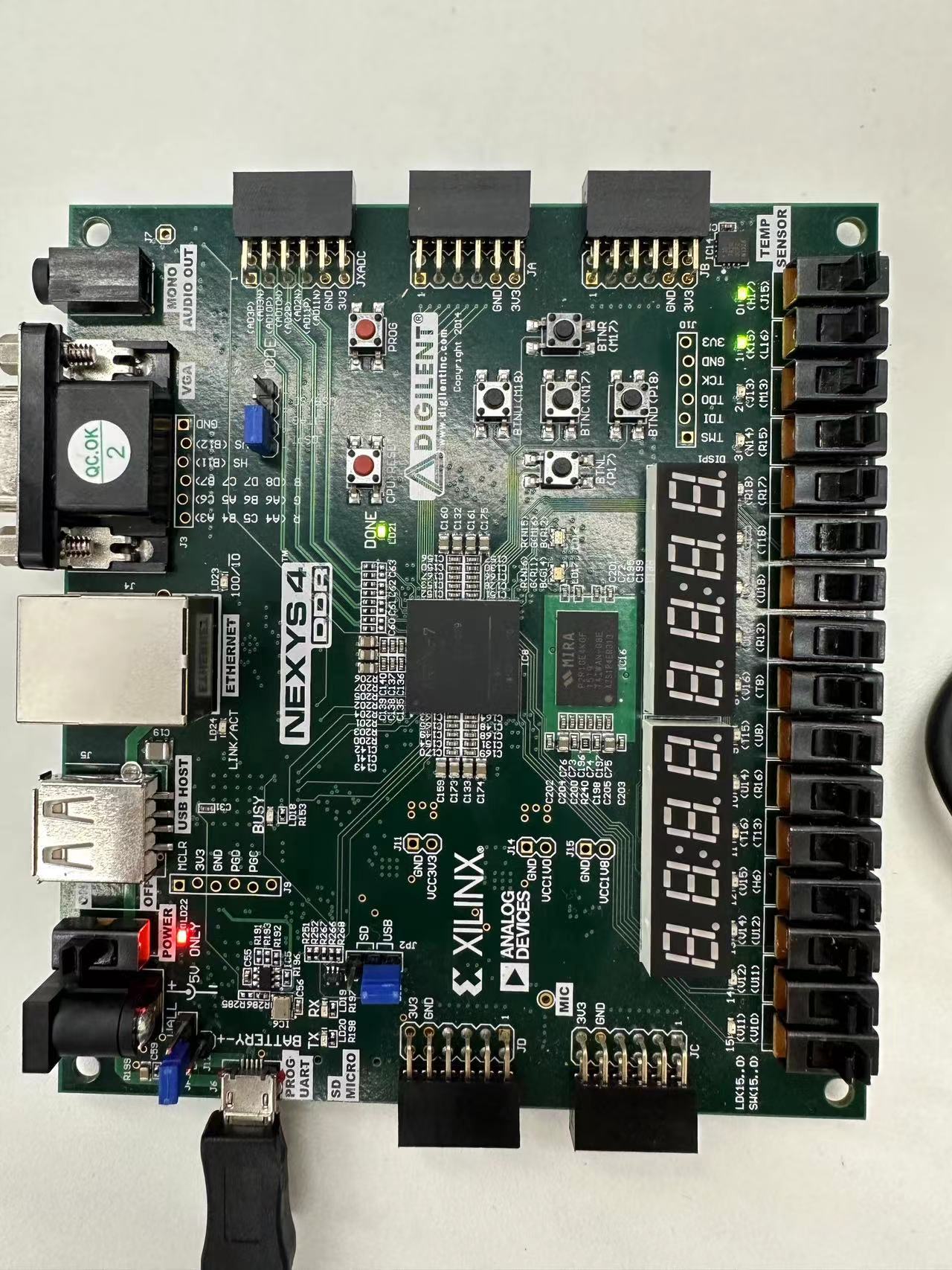

3.选择我们目标要移植到的板子:

这里我们选择的是Nexys4DDR,若Vivado库中没有此板载文件,可以添加对应板载文件到Vivado\2018.2\data\boards\board_files目录下,这里我们给出了Nexys4DDR的开发板文件;

等待创建中~

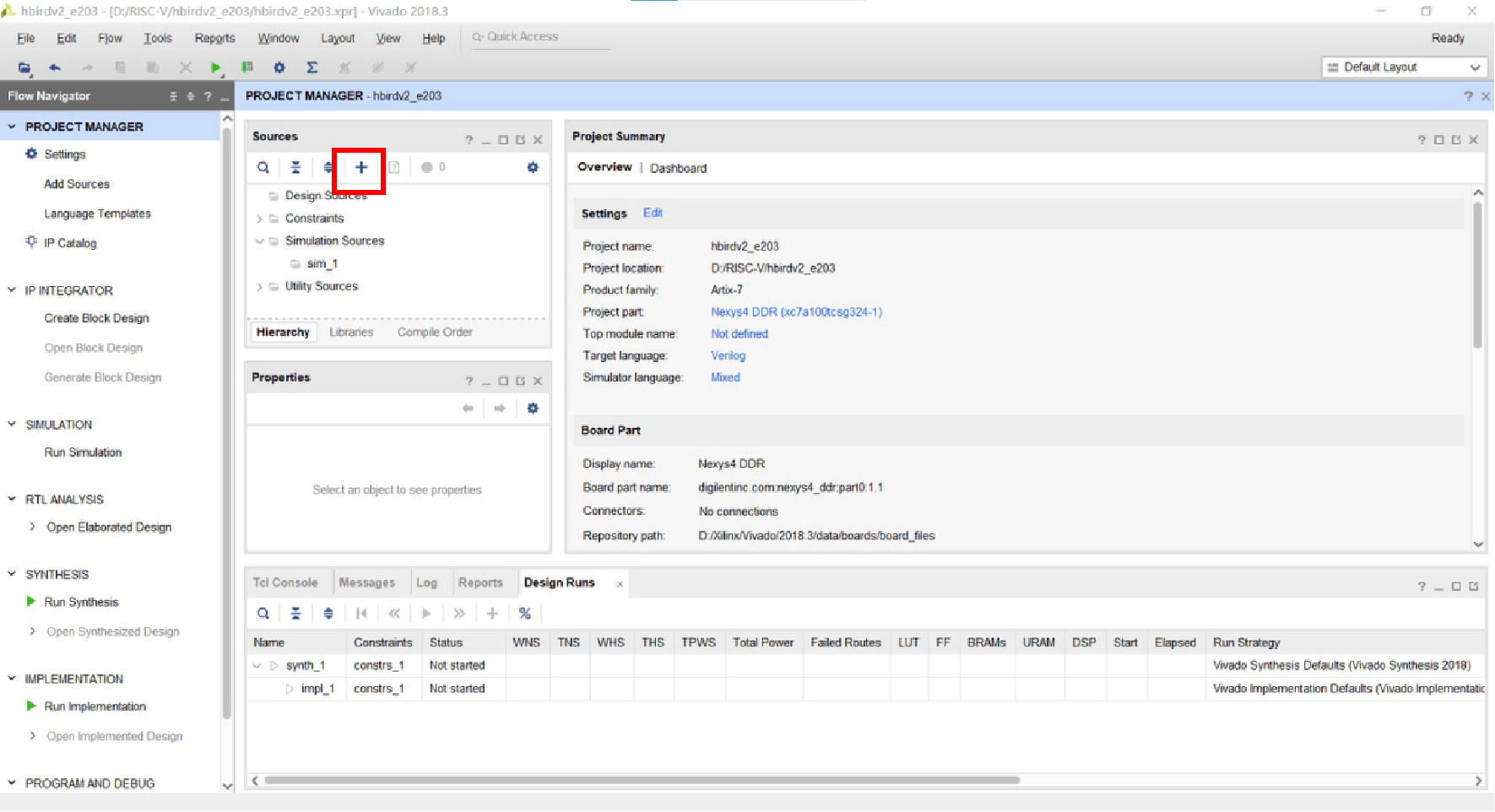

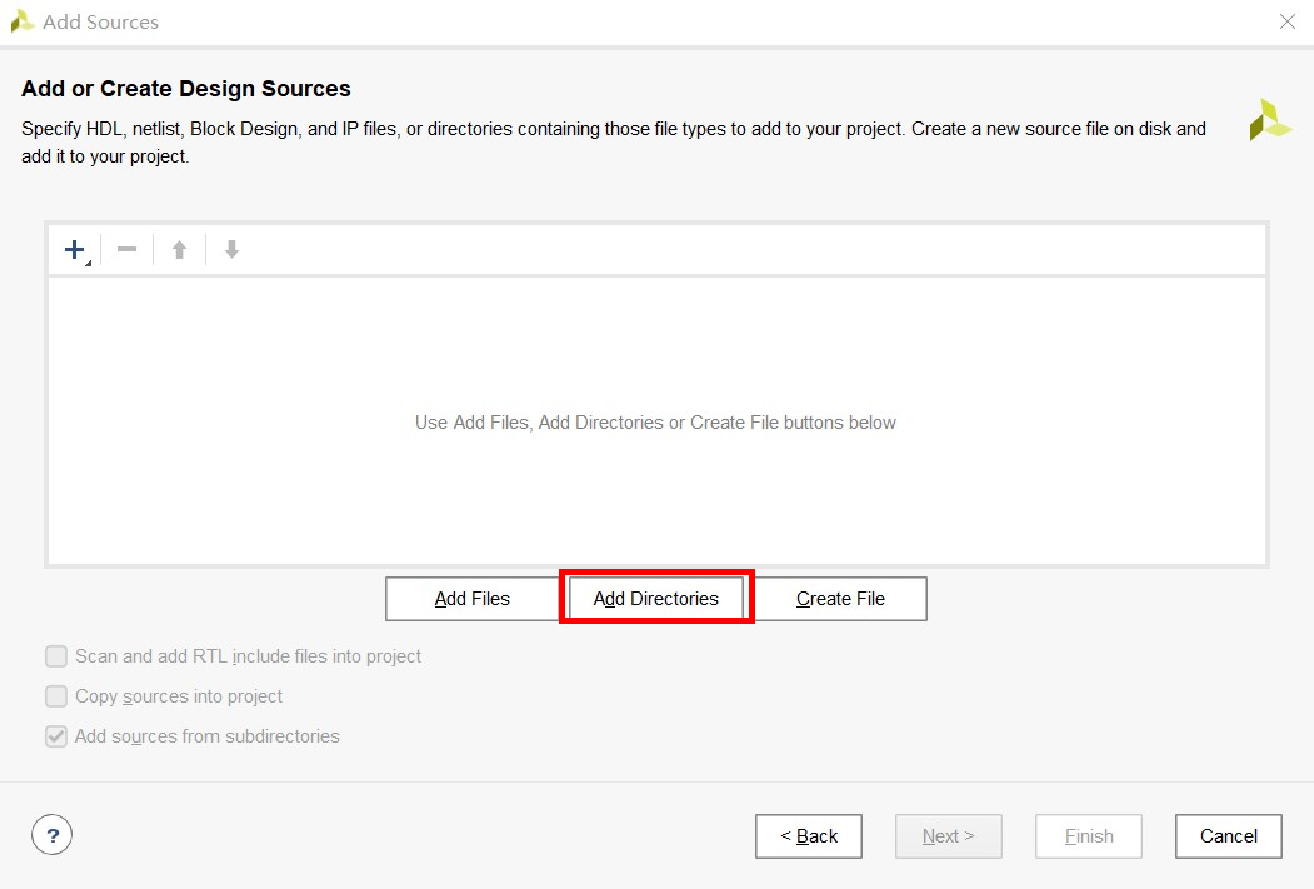

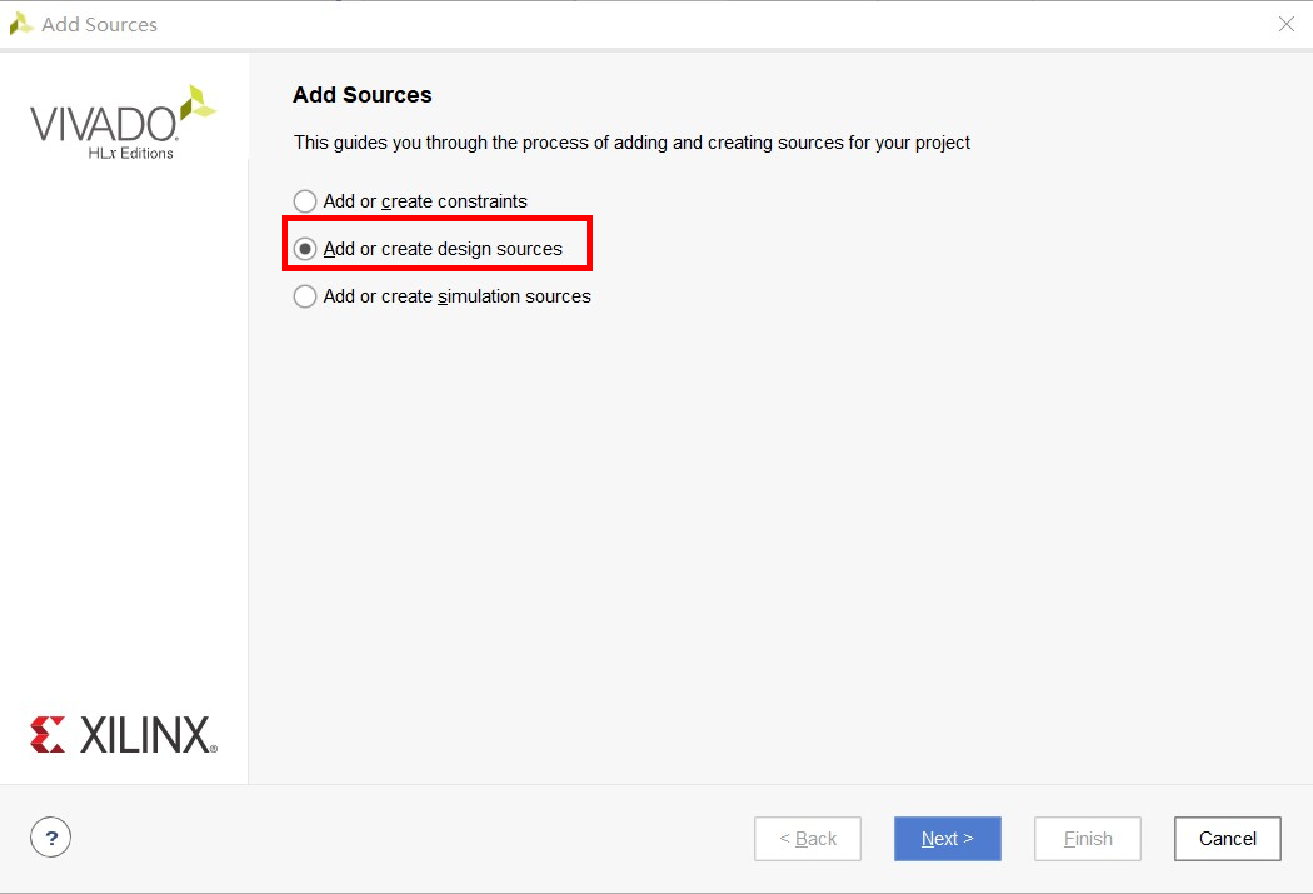

4.添加源文件:

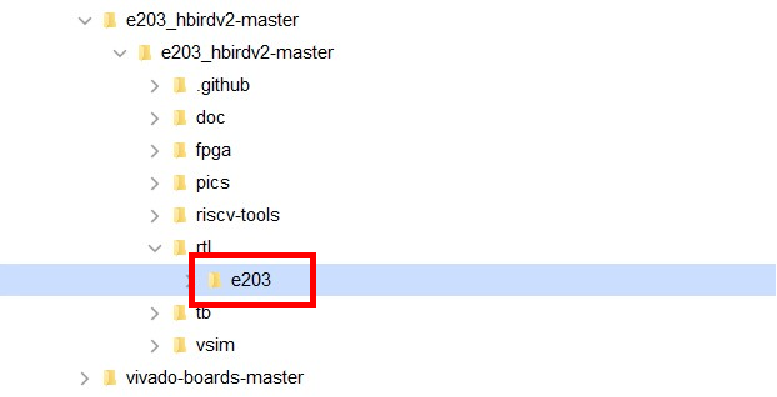

创建工程完成后,单击"+",添加源文件,这里我们选择添加的是文件夹e203(路径为e203_hbirdv2/rtl/e203),Finish完成添加,那两个勾建议可以勾选,会将添加的源文件拷贝到我们的工程目录下,防止对原始文件造成改动;

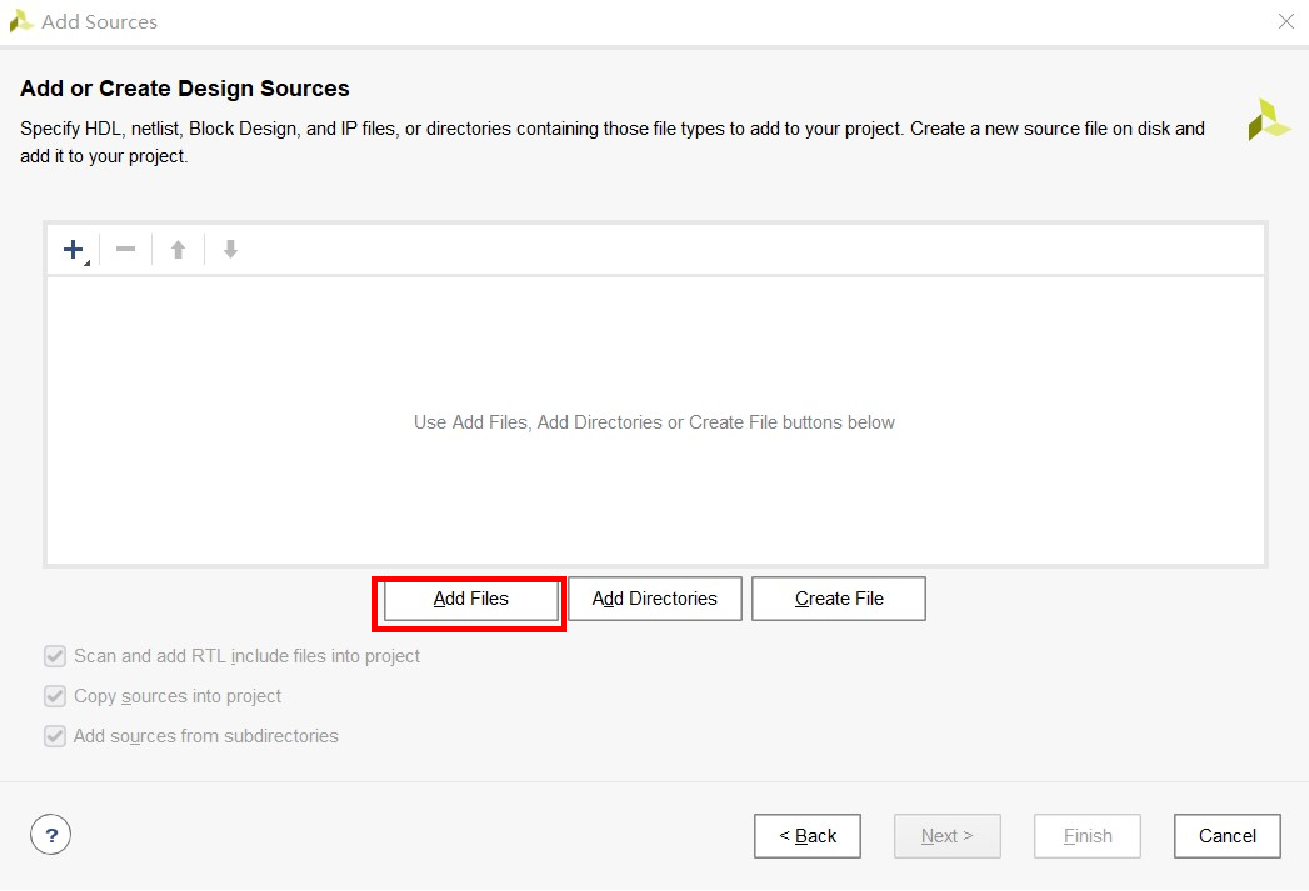

5.添加头文件:

同上操作,找到对应想要移植板子的system.v文件(路径为e203_hbirdv2-master\fpga\mcu200t\system.v),这里选择的是MCU;

6.设置头文件:

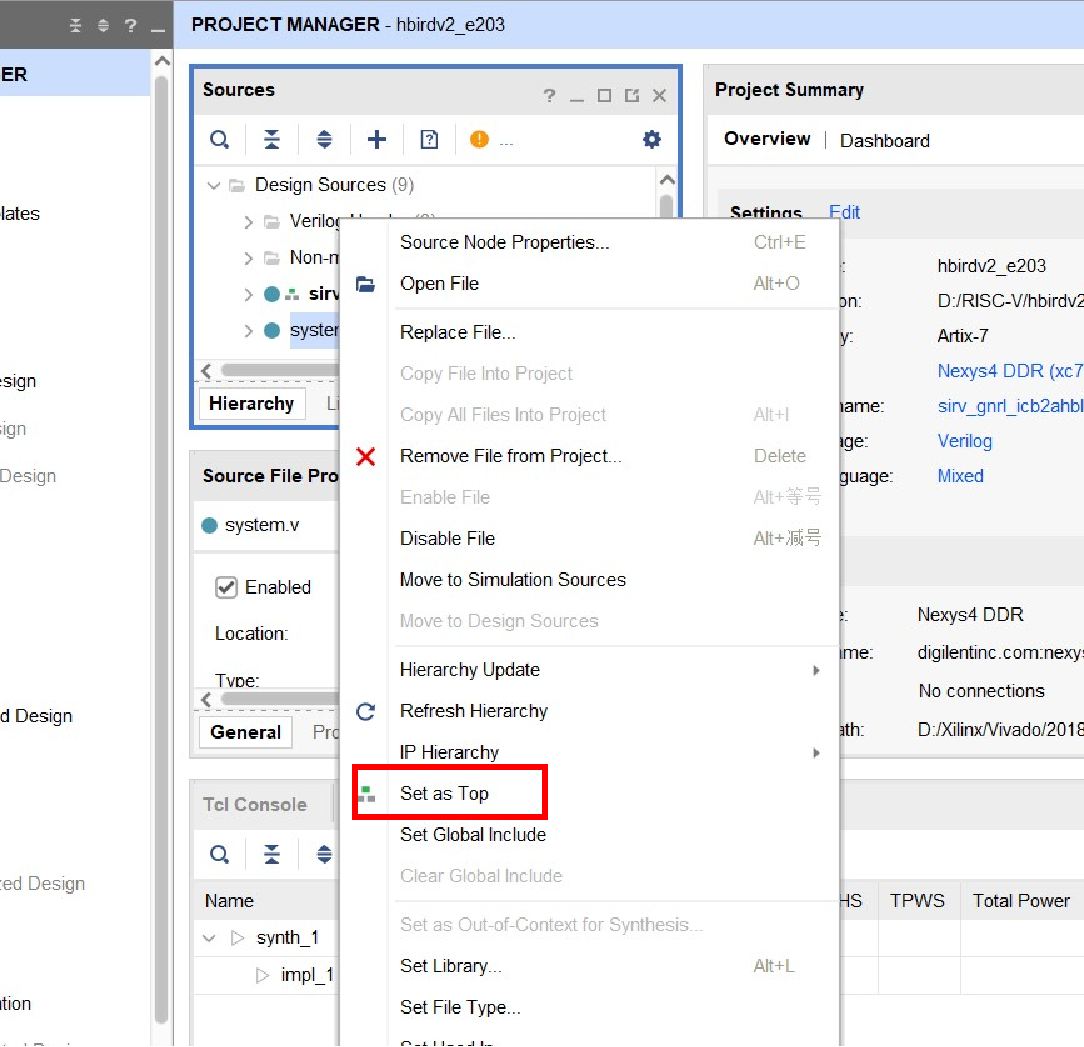

添加完成后,右键点击system.v将其设置为头文件;

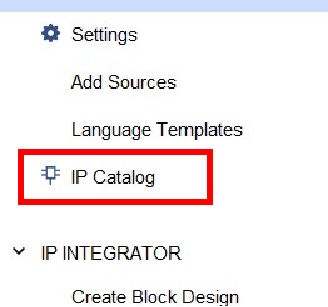

7.调用IP核:

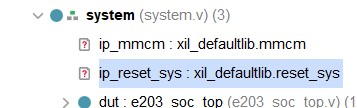

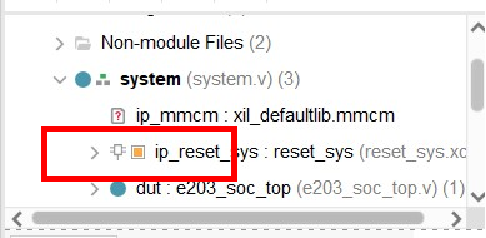

这时,我们会观察到有两个文件有问题,这是由于e203中调用了相应的IP核,我们也要在工程中对应添加;

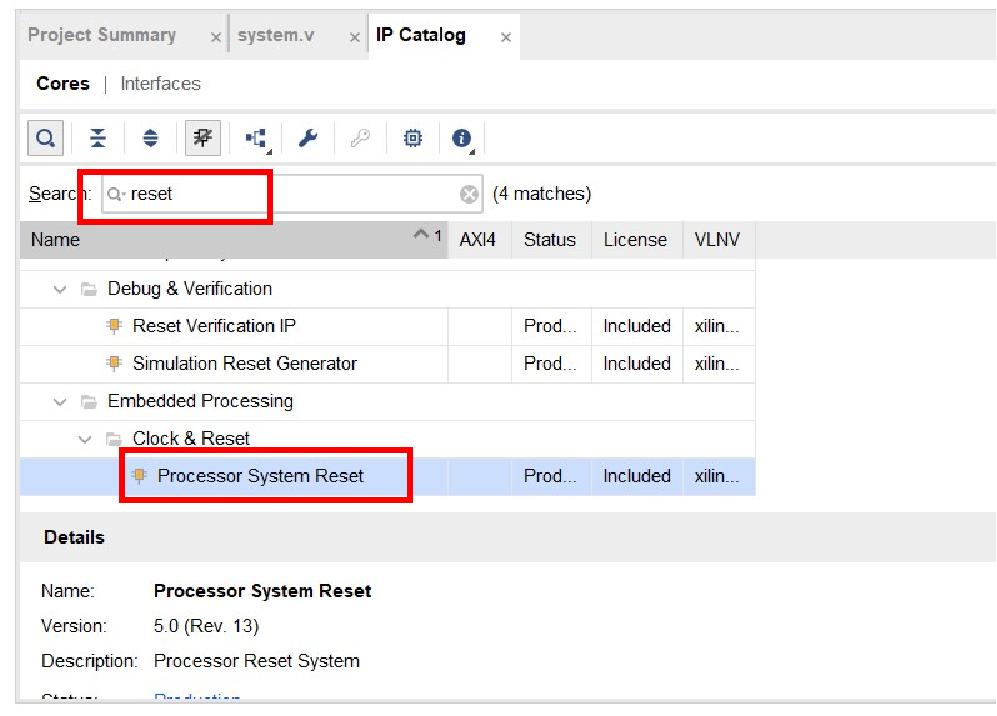

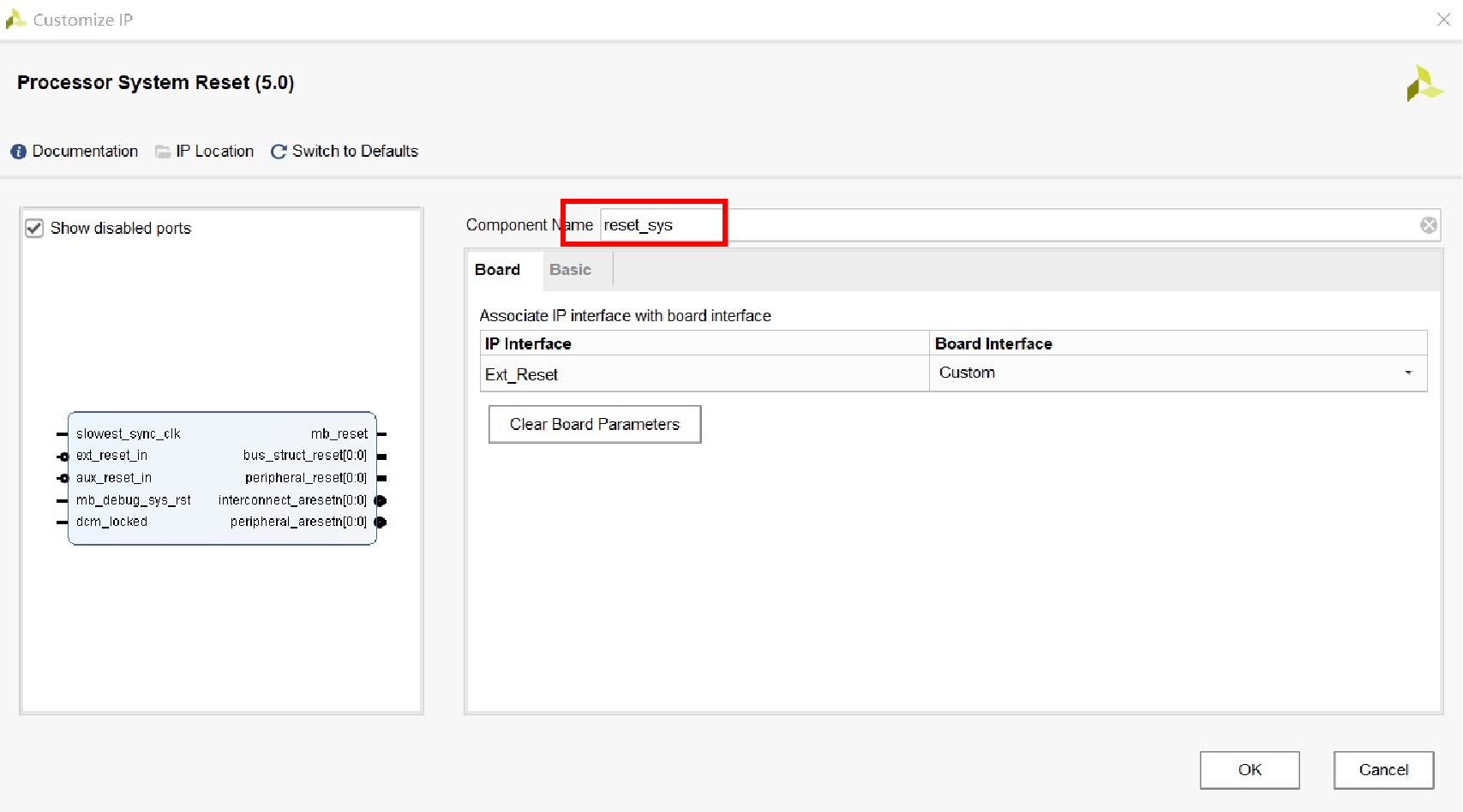

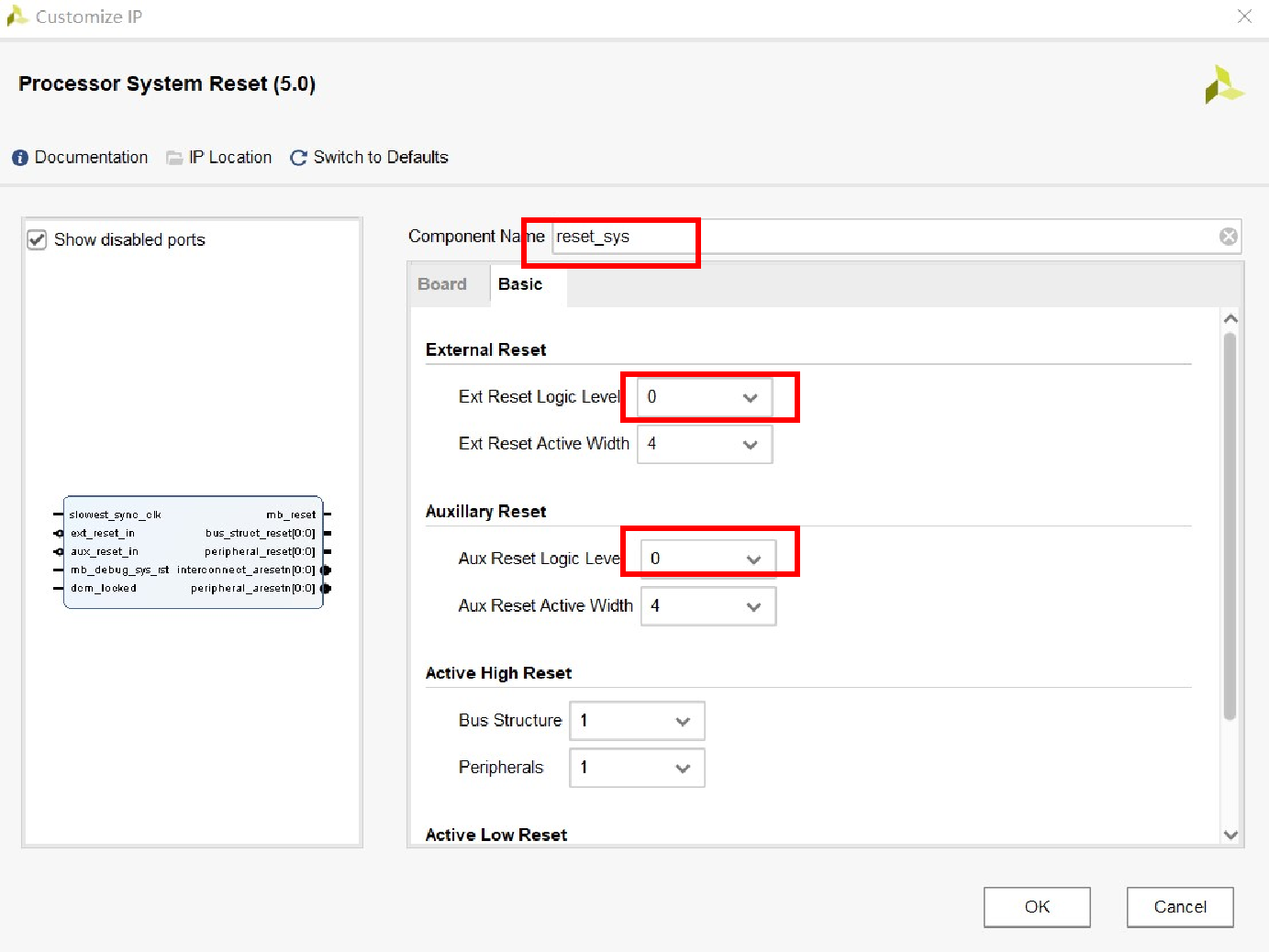

8.添加reset_sys:

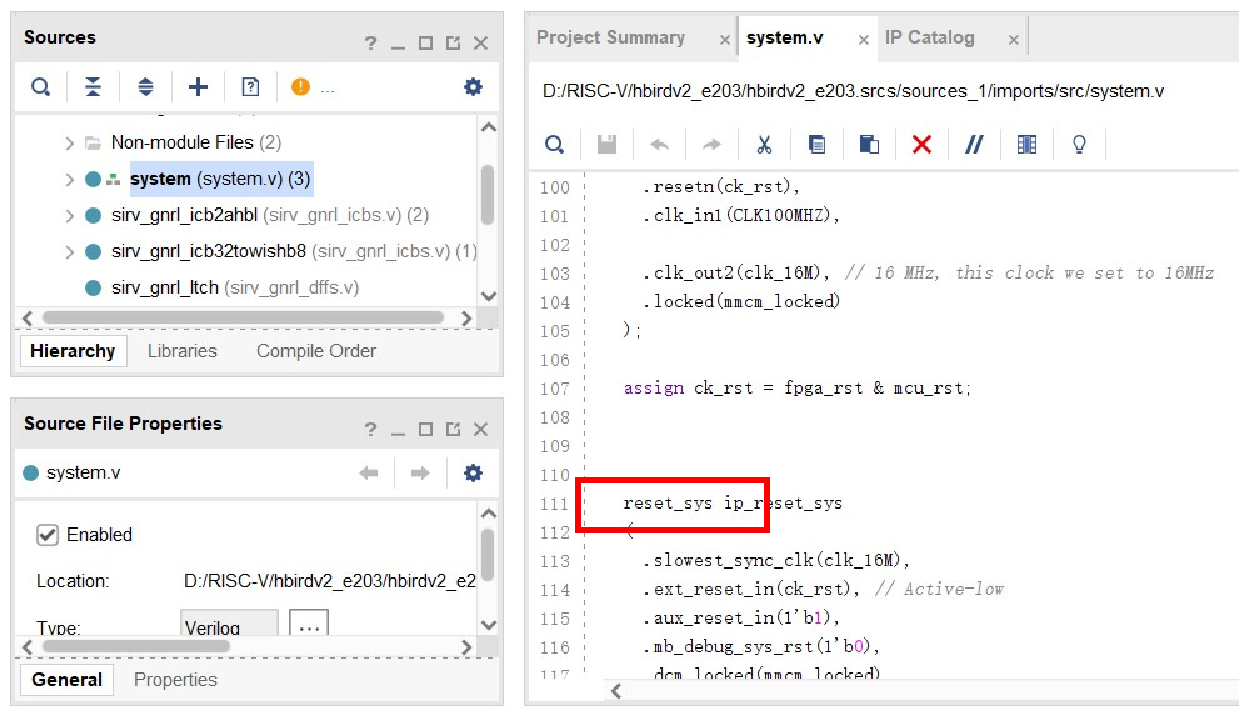

在IP目录中找到对应IP核Processor System Reset,双击将名字改为system.v中的对应名字reset_sys。注意!这里一定要保持名称一致!后修改其复位的优先级为最高,即可完成IP核的调用;

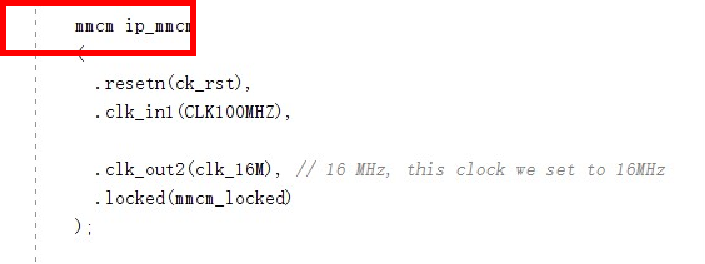

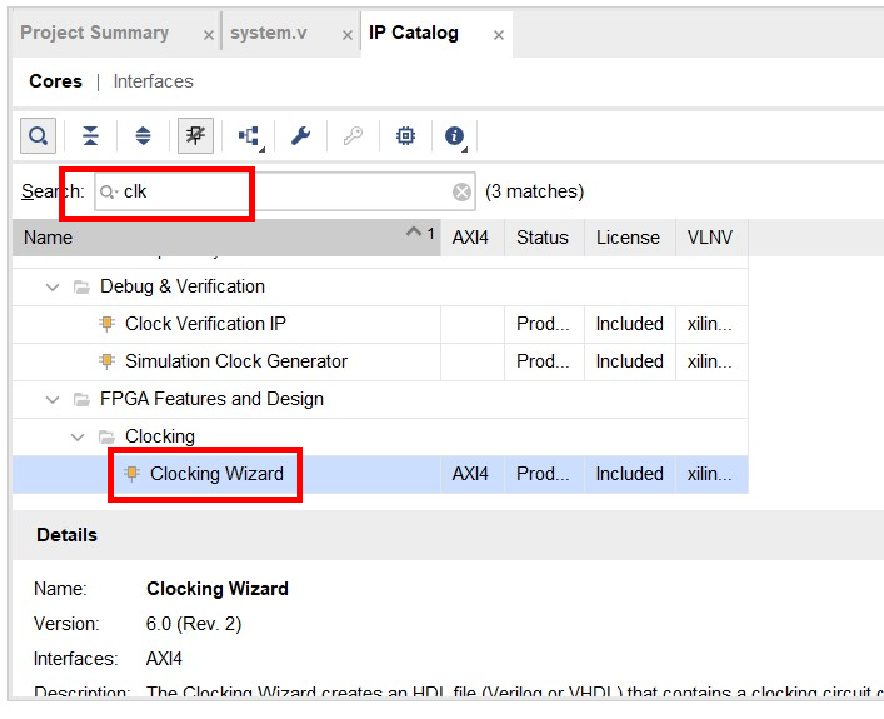

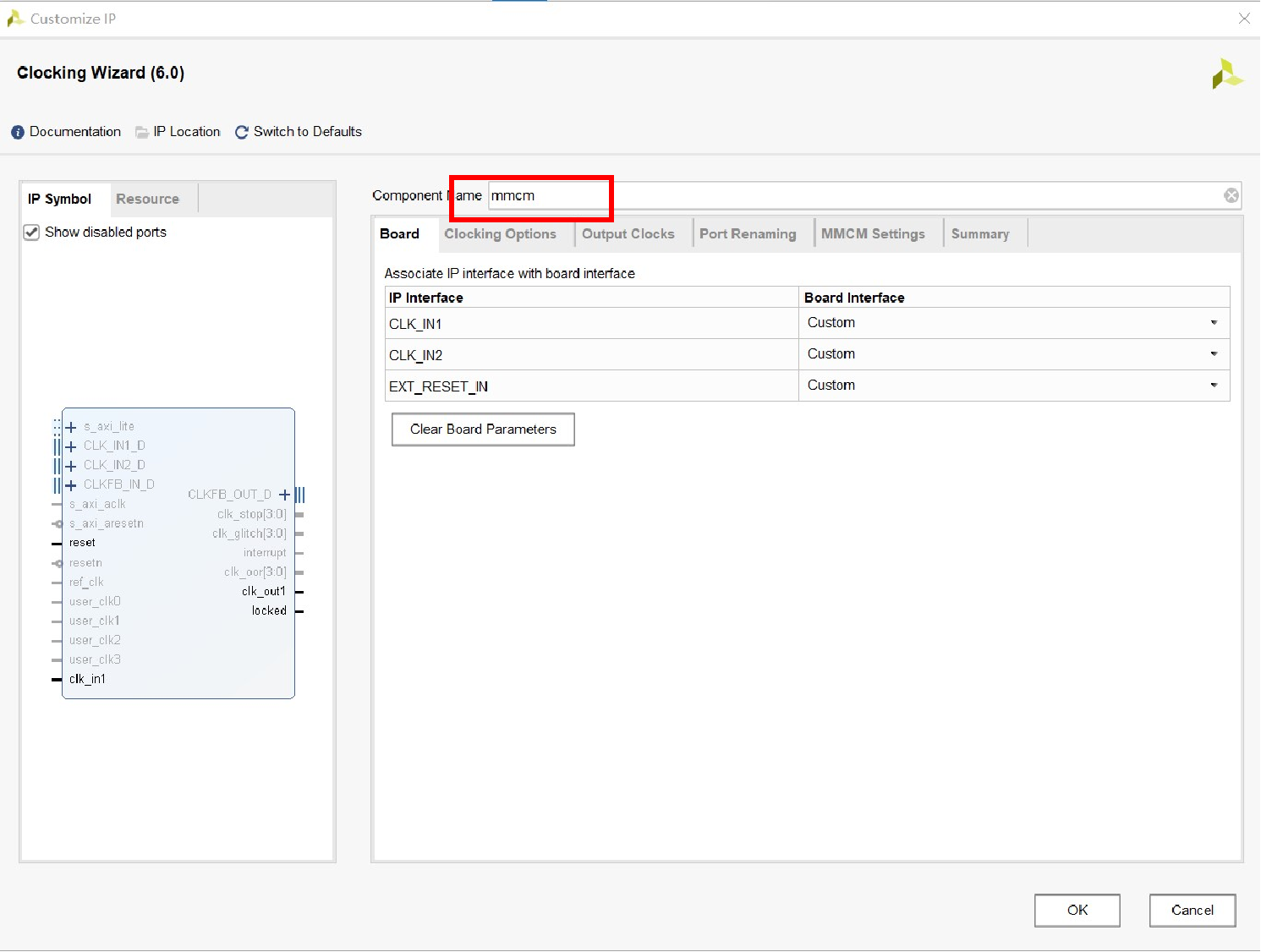

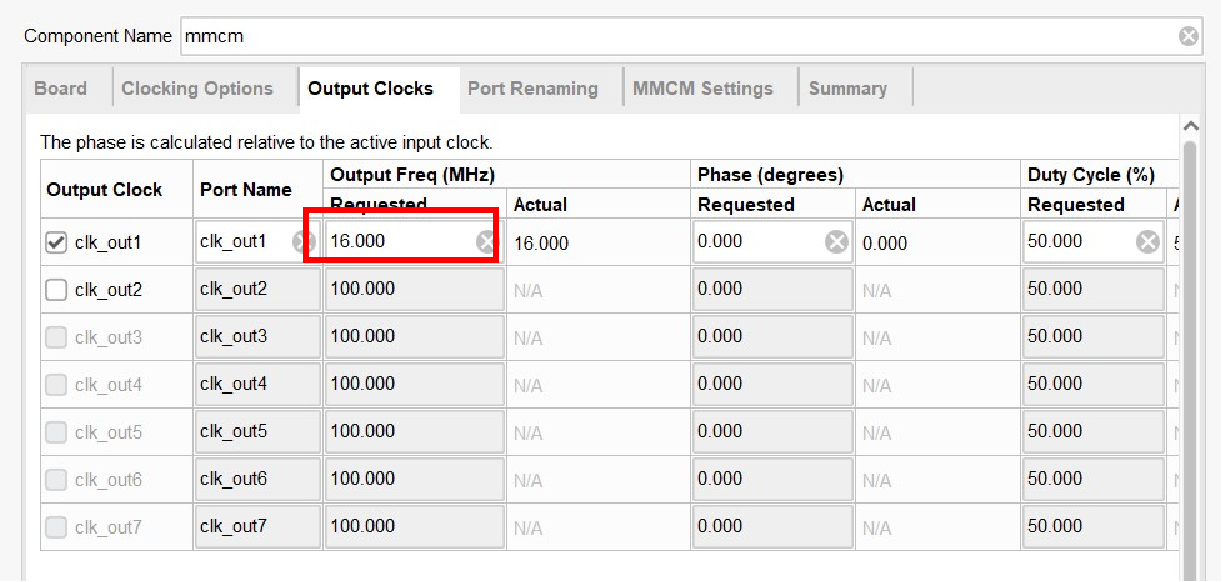

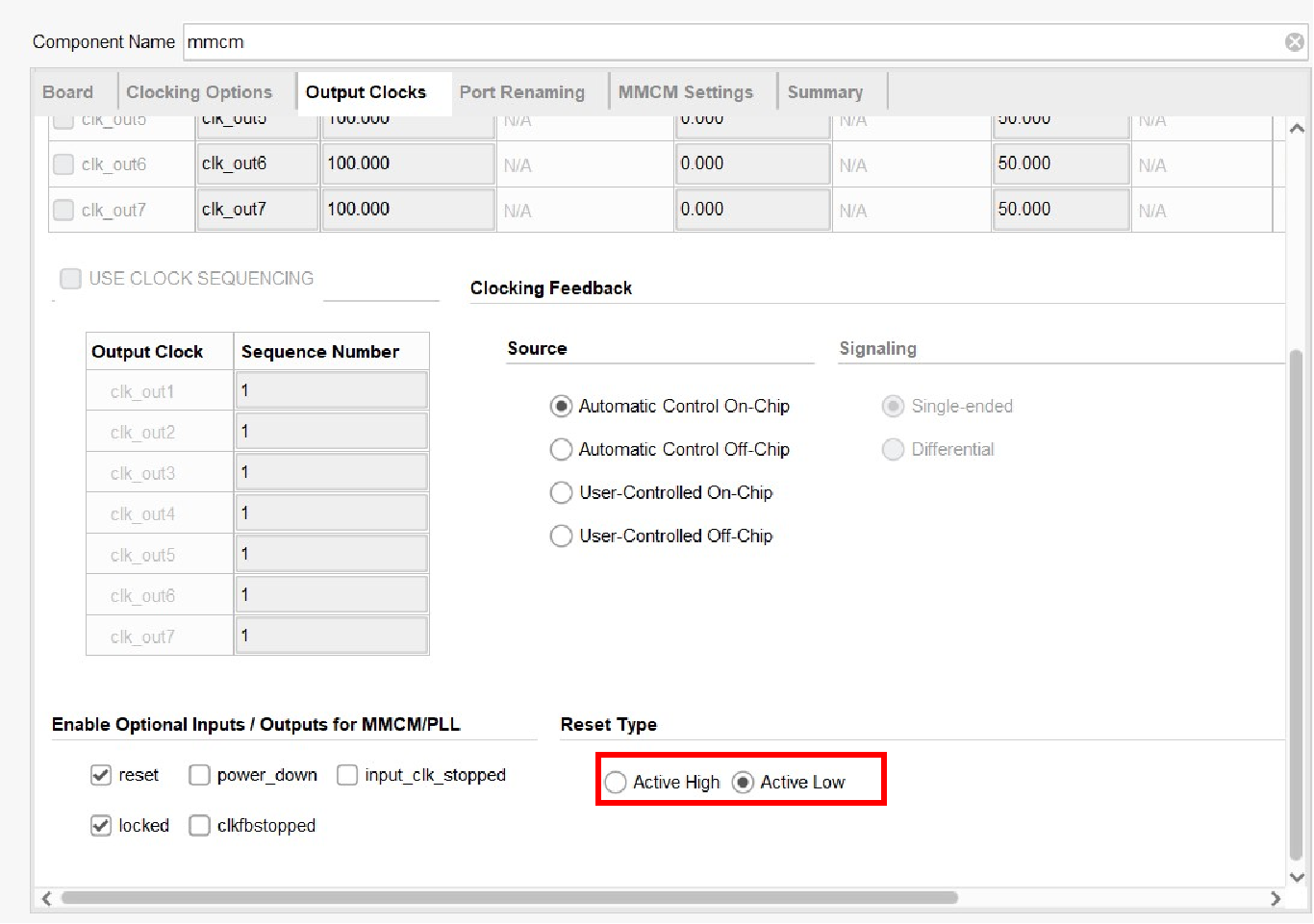

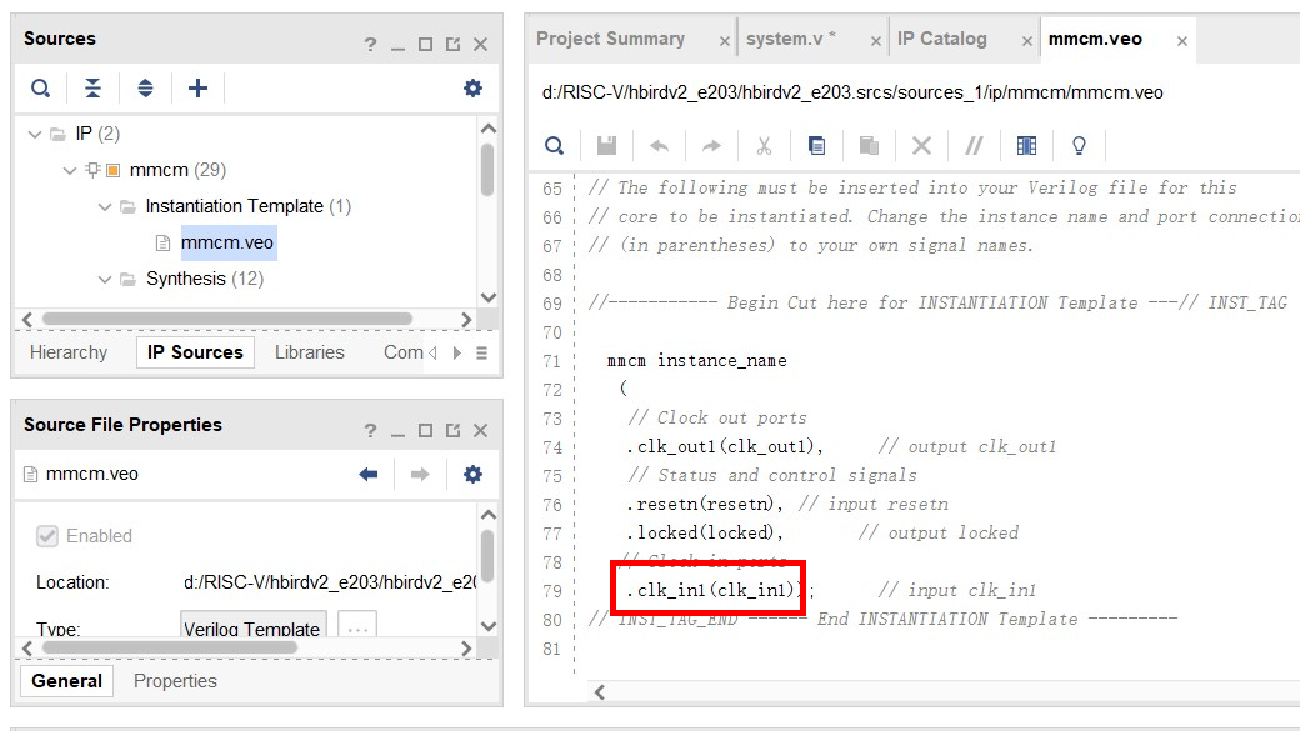

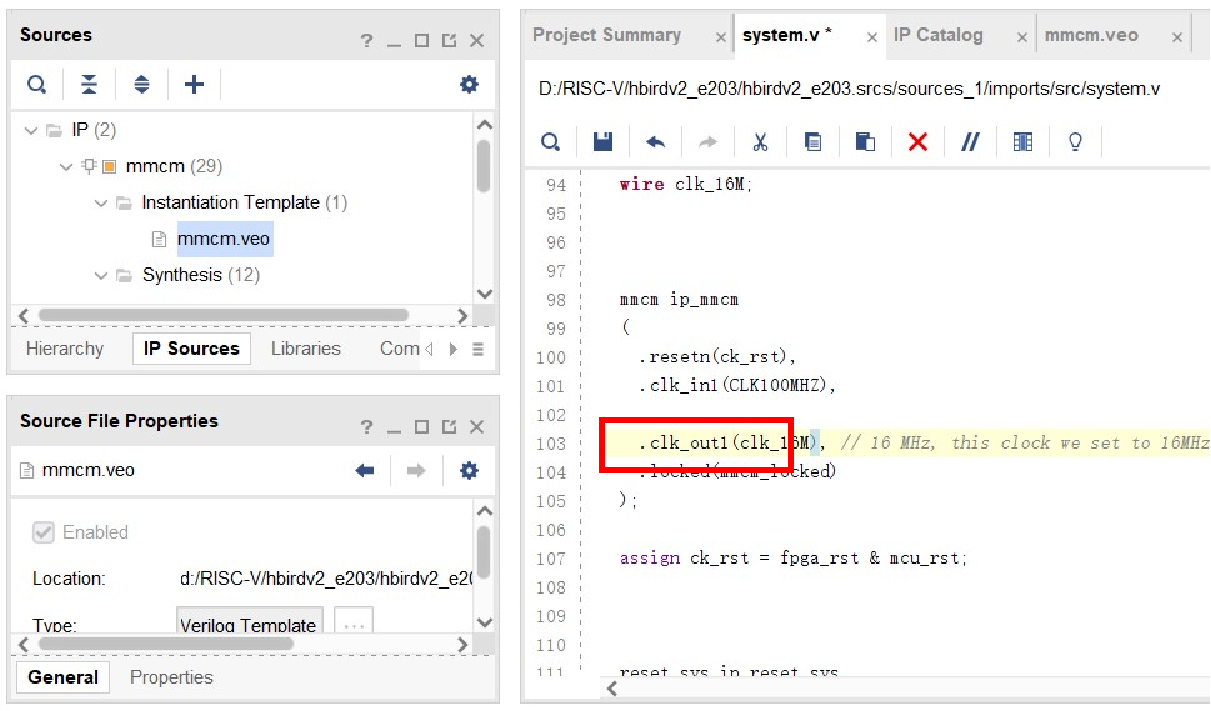

9.添加clk:

在IP目录中找到对应IP核Clocking Wizard,同上操作,将名改为mmcm,修改生成时钟频率为16M,改变复位方式为低电平复位,即可完成IP核的调用;同时应注意这里IP核调用的例化名称应与system.v中保持一致。

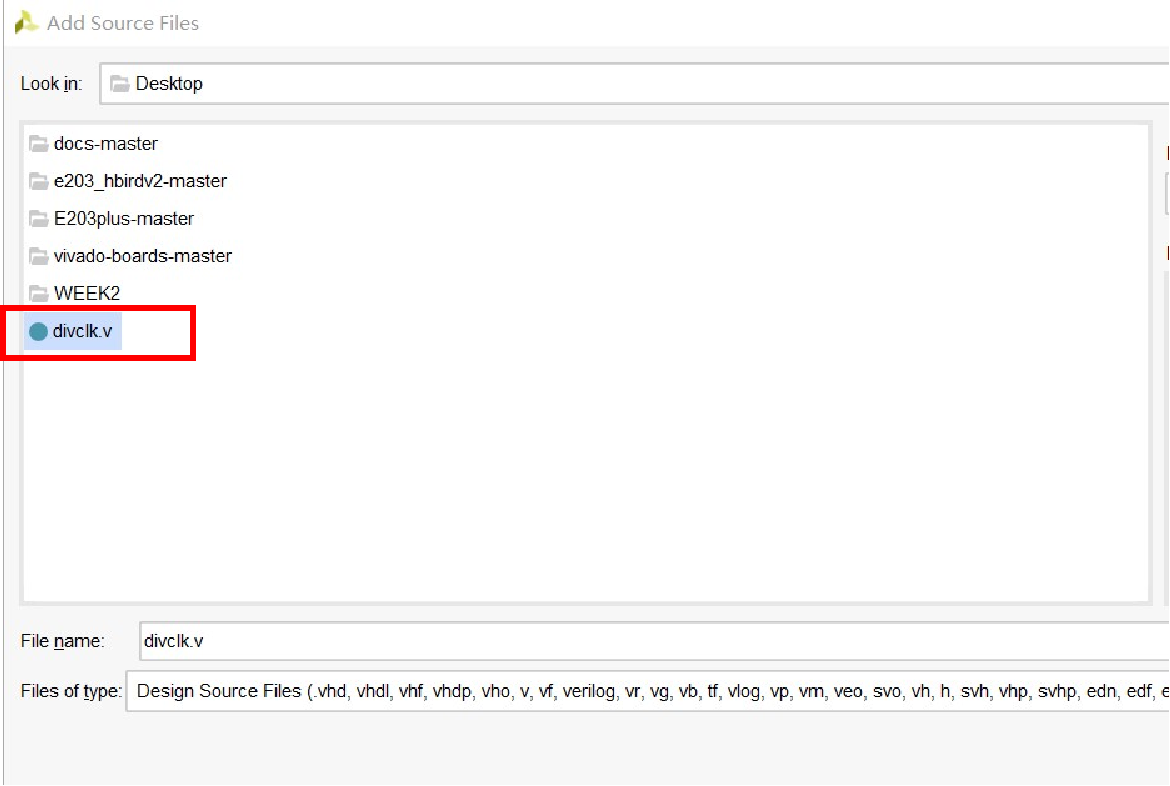

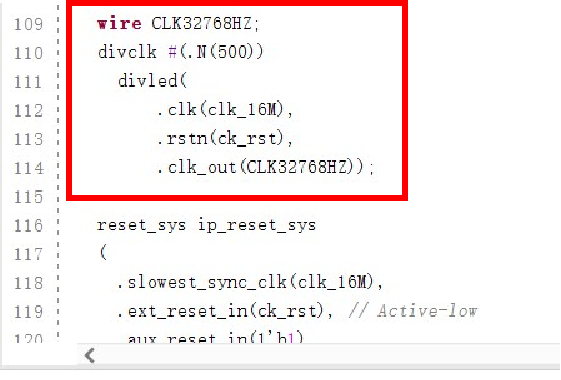

10.添加分频时钟模块:

添加源文件代码,若无可以在资料中找到对应的,调用该模块生成CLK32768KHZ的时钟

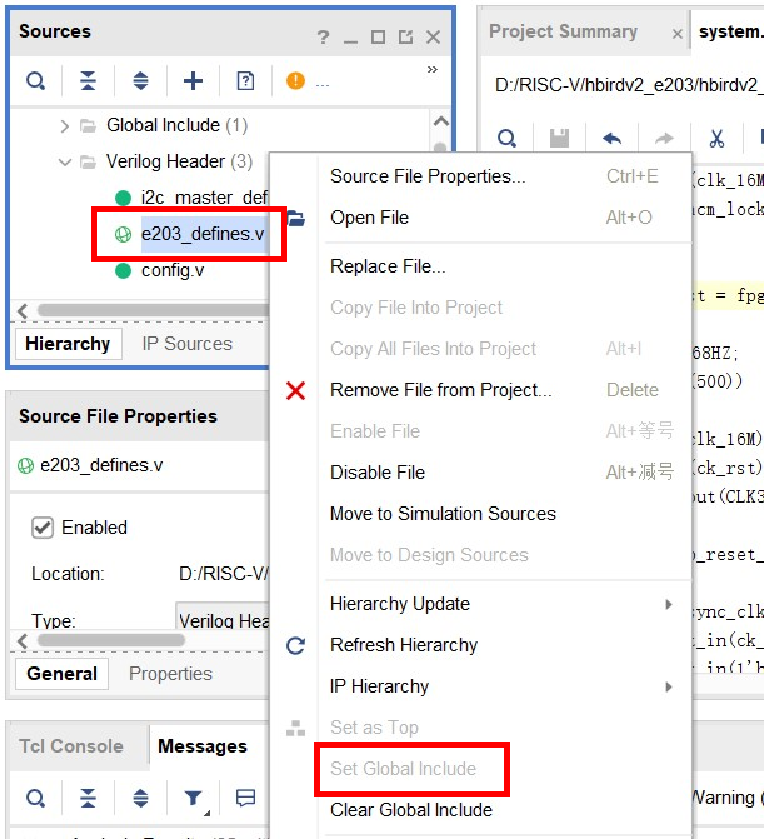

11.修改顶层定义文件:

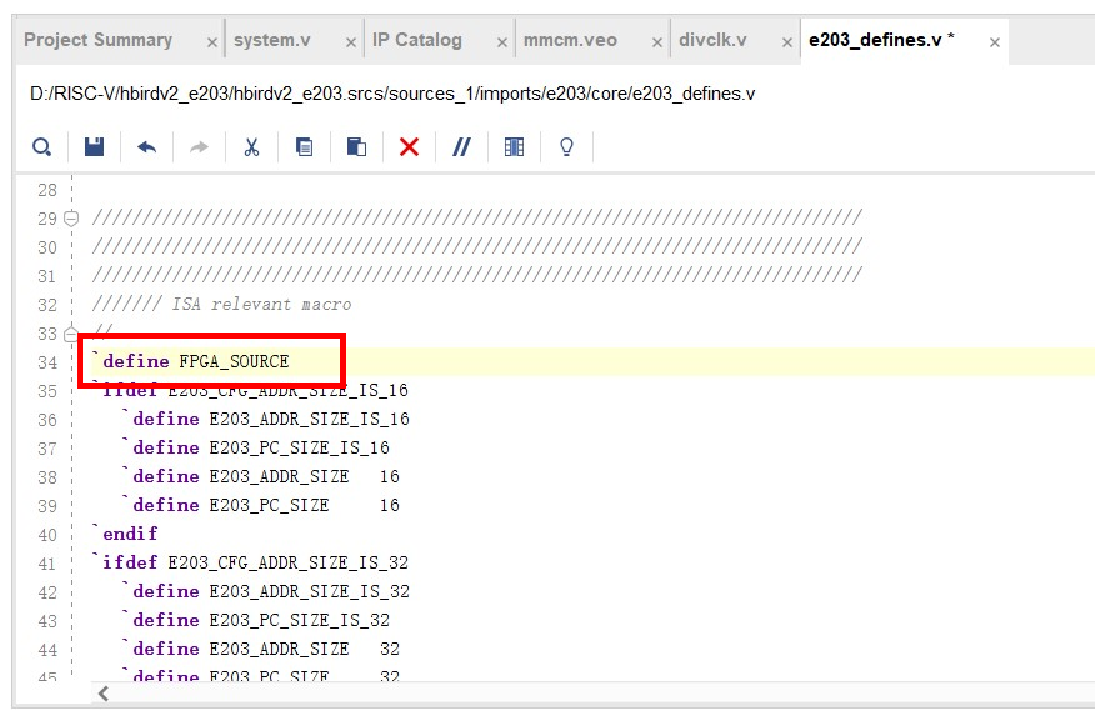

右键单击e203_defines.v,将其设为global define,并在其文件头添加语句:`define FPGA_SOURCE。完成后查看Elaborated Design,若此时报错无法打开e203_defines.v文件,可以在SourceFileProperties中将其对应文件类型改为Verilog Header

12.完成管脚约束:

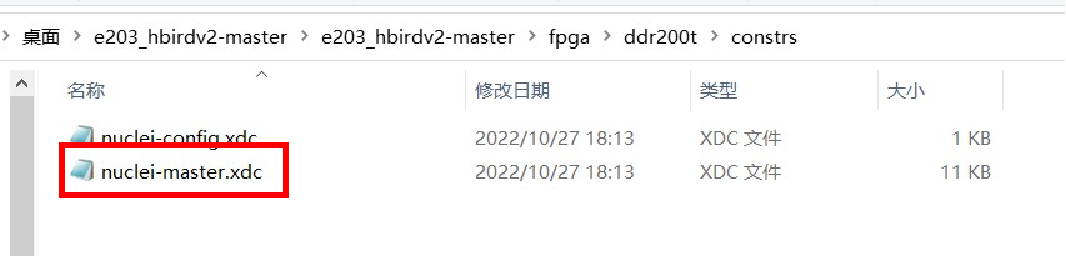

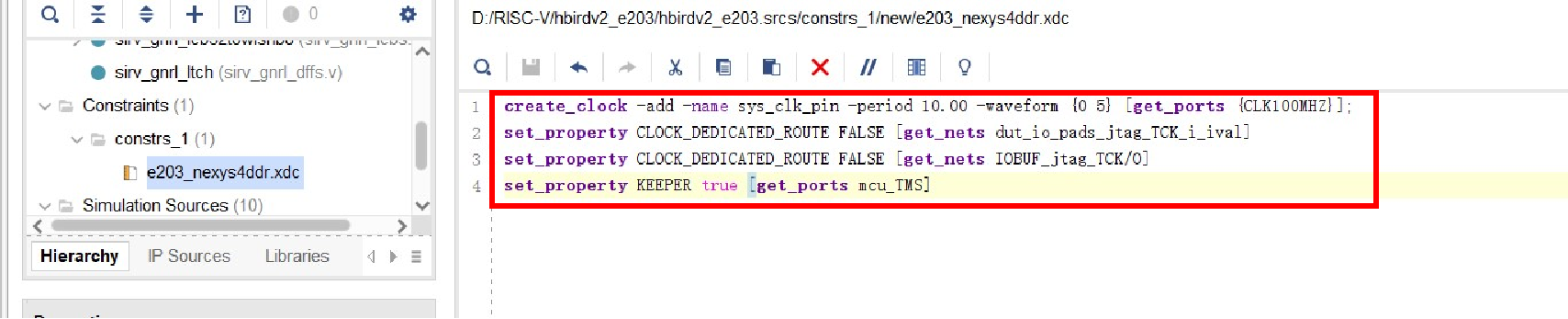

这里提供资料有Nexys4DDR的电路原理图及其约束文件模板,可据此对时钟管脚,SPI引脚,PMU引脚等必要的引脚进行一定约束来简单验证我们能否移植成功。对于管脚约束的完成,我们可以划分成两个模块:xdc约束文件的编写、system.v顶层文件的对应修改。

- xdc约束文件的修改: 主要模块包括:时钟生成及引脚绑定、电源PMU、SPI、JTAG调试,也就是说只要保证了这四个基本模块的引脚约束,就能够实现最基础核心的移植,后续外设的添加可以再自行修改,这里给出约束代码示例如下:

# Clock signalset_property -dict {PACKAGE_PIN E3 IOSTANDARD LVCMOS33} [get_ports CLK100MHZ]# set_property -dict { PACKAGE_PIN F15 IOSTANDARD LVCMOS33 } [get_ports { CLK32768KHZ }];create_clock -period 10.000 -name sys_clk_pin -waveform {0.000 5.000} -add [get_ports CLK100MHZ]# set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets dut_io_pads_jtag_TCK_i_ival]# set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets IOBUF_jtag_TCK/O] # Resetset_property -dict {PACKAGE_PIN C12 IOSTANDARD LVCMOS33} [get_ports fpga_rst]set_property -dict {PACKAGE_PIN M18 IOSTANDARD LVCMOS33} [get_ports mcu_rst] # QSPI interfaceset_property -dict {PACKAGE_PIN K17 IOSTANDARD LVCMOS33} [get_ports {qspi0_dq[0]}]set_property -dict {PACKAGE_PIN K18 IOSTANDARD LVCMOS33} [get_ports {qspi0_dq[1]}]set_property -dict {PACKAGE_PIN L14 IOSTANDARD LVCMOS33} [get_ports {qspi0_dq[2]}]set_property -dict {PACKAGE_PIN M14 IOSTANDARD LVCMOS33} [get_ports {qspi0_dq[3]}]set_property -dict {PACKAGE_PIN L13 IOSTANDARD LVCMOS33} [get_ports qspi0_cs] # JTAG connection# set_property -dict { PACKAGE_PIN E13 IOSTANDARD LVCMOS33 } [get_ports { mcu_TDO }];# set_property -dict { PACKAGE_PIN E10 IOSTANDARD LVCMOS33 } [get_ports { mcu_TCK }];# set_property -dict { PACKAGE_PIN E11 IOSTANDARD LVCMOS33 } [get_ports { mcu_TDI }];# set_property -dict { PACKAGE_PIN E12 IOSTANDARD LVCMOS33 } [get_ports { mcu_TMS }]; # pmu_wakeupset_property -dict {PACKAGE_PIN H17 IOSTANDARD LVCMOS33} [get_ports pmu_paden]set_property -dict {PACKAGE_PIN K15 IOSTANDARD LVCMOS33} [get_ports pmu_padrst]set_property -dict {PACKAGE_PIN N17 IOSTANDARD LVCMOS33} [get_ports mcu_wakeup] set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 4 [current_design]set_property BITSTREAM.CONFIG.SPI_FALL_EDGE YES [current_design]

-

system.v中对应文件的修改:顶层模块中代码功能划分十分规整,对于不需要的模块如GPIO等直接注释掉即可。

-

如恰好我们移植的是同一块板子,那么恭喜你,我已经在资料包里准备好了两份文件,直接导入工程即可😊

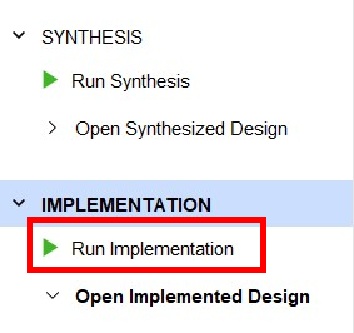

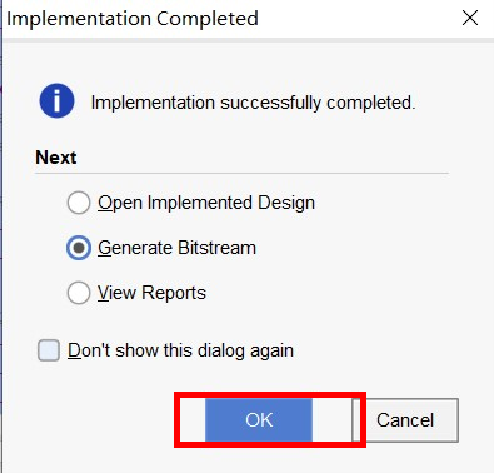

13.综合并生成比特流文件:

点击implementation 进行工程的综合,这个时间会比较漫长,可以先去吃个晚饭😊!

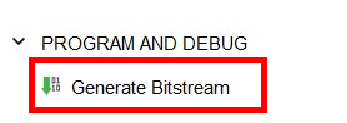

综合完成后点击**Generate Bitstream**生成比特流文件,这步是将我们的工程文件生成二进制比特流文件,以便后续烧入板子。

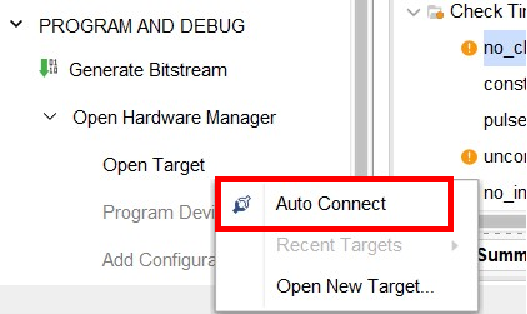

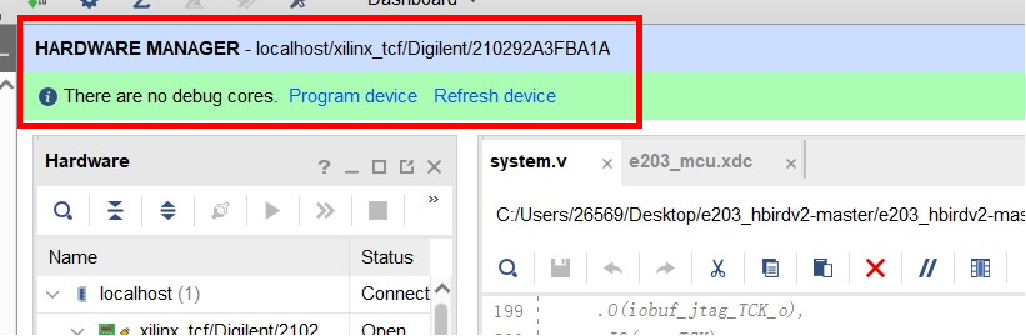

14.连接开发板:

将开发板与PC正确连接并供电,在Vivado中打开HardwareManager,使用Auto Connect自动连接板子,如此步报错,或一直无法连接成功,可能是由于电脑未安装相关驱动造成,可以在 \Xilinx\Vivado\2018.3\data\xicom\cable_drivers\nt64 目录下找到install_diligent.exe双击安装,如果此时还不能自动连接,就下载一个驱动精灵什么的让他解决一下吧~(虽然那个软件看起来很“金山毒霸”\doge)

连接成功后的结果如下图所示。

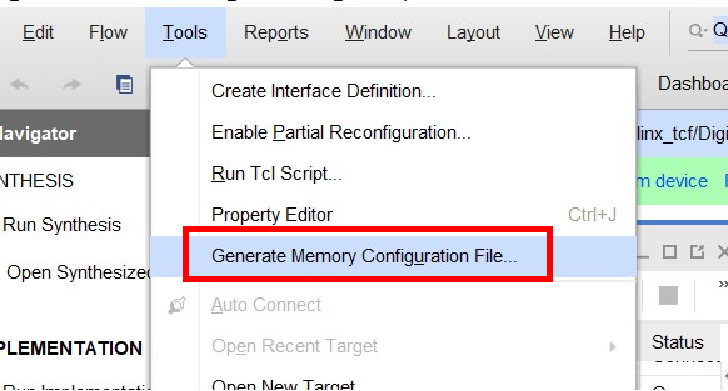

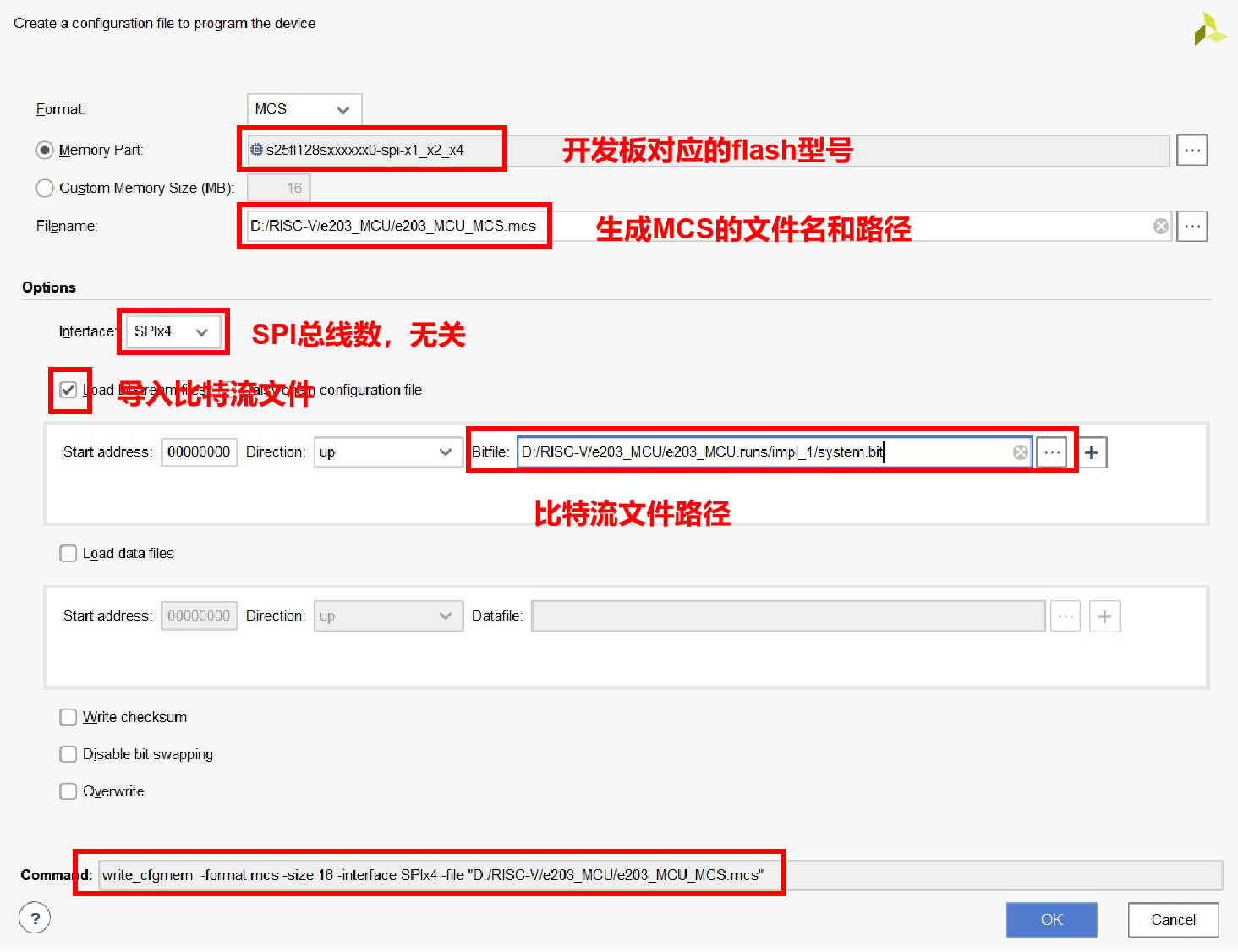

15.生成MCS文件:

单击Vivado上方工具栏的Tools->Generate Memory Configuration Files,弹出的窗口如下所示,进行如图所示的配置,即可在当前工程目录下生成MCS文件。

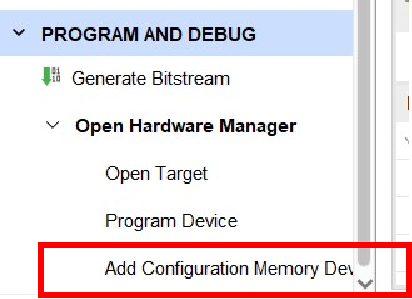

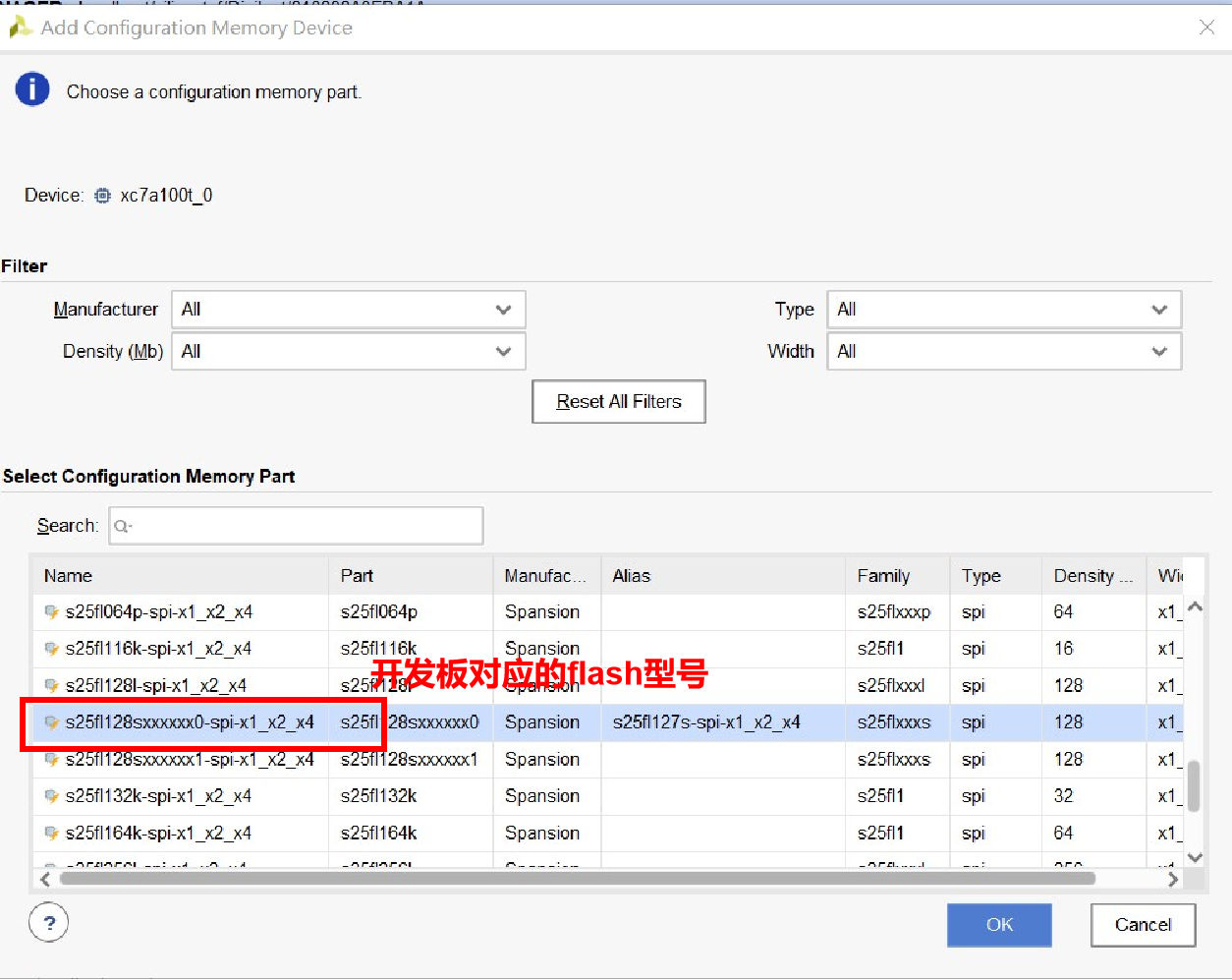

16.导入flash装置:

在左侧功能栏最末尾找到Add Configuration Memory Device,填出的窗口如图所示,进行如图所示的配置,即可导入相应的开发板flash。

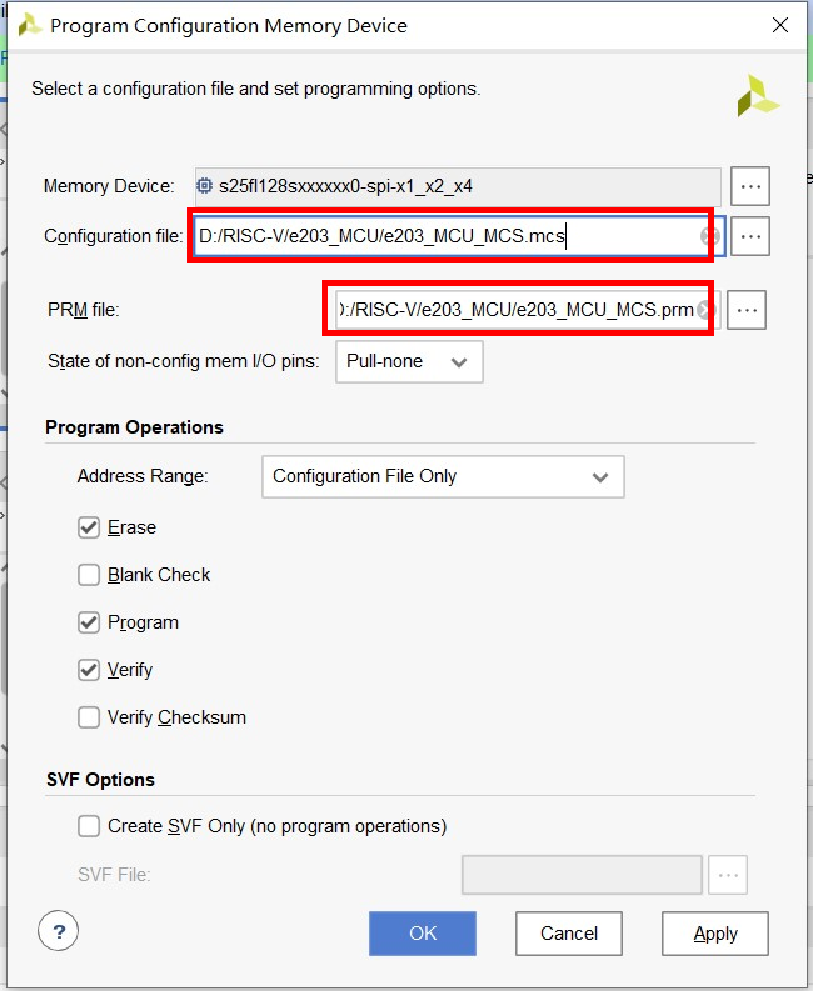

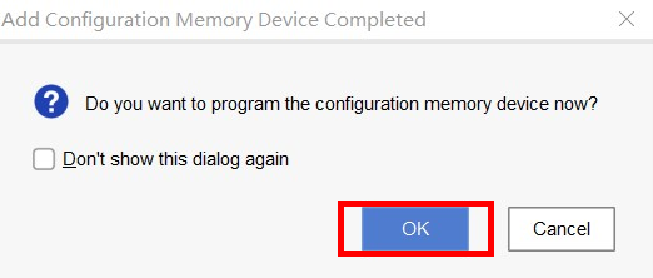

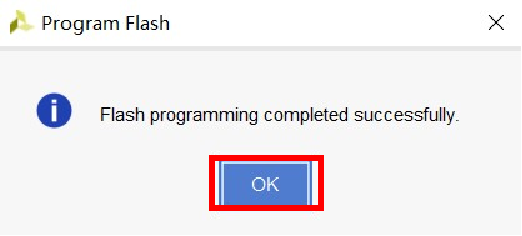

17.烧入开发板:

完成装置选择后,将会自动弹出一个询问你是否现在就要Program的一个窗口,选择是,则来到以下界面,添加入我们前面生成的MCS文件即可,等待---,即完成了我们的内核固化过程。

写在最后的话:

花了很多精力才完成了整个的移植,在网上也找了很多教程,或是因为版本不一致,或是一些细致之处没有说明,踩了很多坑,走了很多弯路。写这篇教程时,已经是我第五次尝试移植了,可能还存在不够细致之处,或者上下文逻辑不连贯之处,如有问题指出,欢迎大家留言,我每天都会看的!!大家一起进步!!

Recommend

About Joyk

Aggregate valuable and interesting links.

Joyk means Joy of geeK