JEDEC或放宽HBM4高度限制,在现有的键合技术中实现16层堆叠

source link: https://www.expreview.com/92768.html

Go to the source link to view the article. You can view the picture content, updated content and better typesetting reading experience. If the link is broken, please click the button below to view the snapshot at that time.

JEDEC或放宽HBM4高度限制,在现有的键合技术中实现16层堆叠

吕嘉俭发布于 2024-3-14 12:19

本文约 570 字,需 1 分钟阅读

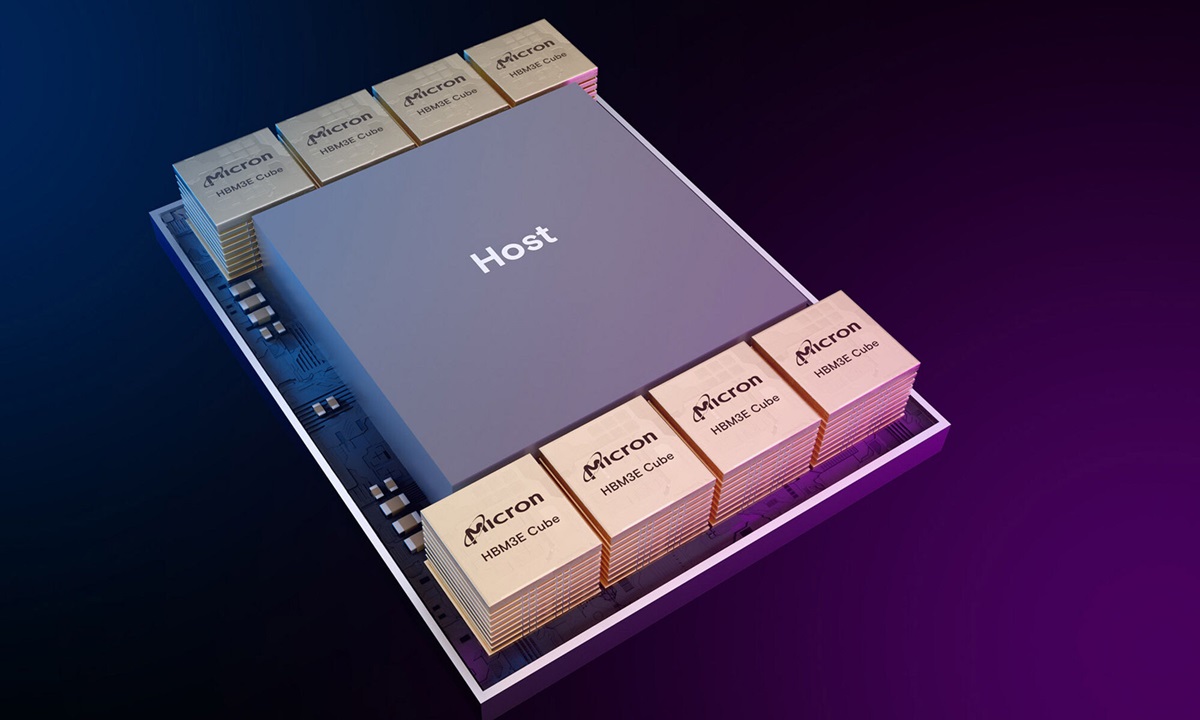

近年来,人工智能(AI)、高性能计算(HPC)和PC一直在推动高性能DRAM产品的研发,市场对HBM类DRAM的需求也在迅速增长。从去年下半年起,就不断传出有关下一代HBM4的消息,三星、SK海力士和美光三家主要存储器制造商都加大了这方面的投入,以加快研发的进度。

据ZDNet报道,JEDEC固态存储协会可能会放宽HBM4在高度方面的要求,也就是最高的720微米的限制。为了降低三星、SK海力士和美光的制造难度,传闻JEDEC可能将12层及16层堆叠的HBM4高度放宽至775微米,这意味着存储器制造商可以在现有的键合技术中实现16层堆叠,无需转向新的混合键合技术。

目前无论是三星的TC NCF技术还是SK海力士的MR-RUF技术,都是使用凸块实现层与层之间的连接。上个月三星宣布,已开发出业界首款HBM3E 12H DRAM,从过去的8层堆叠提高至12层堆叠,而且通过对TC NCF材料的优化,已经将间隙减低至7微米。不过要实现16层堆叠,厚度必然会继续增加,现有的技术在原限定高度下很难实现这样的操作。

混合键合技术不需要凸块,通过板载芯片和晶圆直接键合,让层与层之间更加紧密,以减少封装厚度。不过混合键合技术尚未成熟,而且相比现有的键合技术过于昂贵,因此现阶段存储器制造商还不太愿意采用。

随着JEDEC同意放宽HBM4的高度限制要求,一方面为混合键合技术争取到了更多的开发时间,另一方面也加快了HBM4的商业化进程。

Recommend

About Joyk

Aggregate valuable and interesting links.

Joyk means Joy of geeK