苹果,玩转先进封装

source link: https://www.36kr.com/p/2376046894180352

Go to the source link to view the article. You can view the picture content, updated content and better typesetting reading experience. If the link is broken, please click the button below to view the snapshot at that time.

苹果,玩转先进封装

2017 年 11 月21日,时任台积电董事长的张忠谋在台下默默鼓掌,这一天的主角,不是声名赫赫的他,而是此前默默无名的余振华。

接过奖项的他,指了指着一旁记者手中的iPhone说:“这个就有InFO(整合扇出型封装),从iPhone 7就开始了,现在继续在用,iPhone 8、iPhone X,以后别的手机也会开始用这个技术。”

这里提到的InFO,即先进封装中的一种,正是它让台积电轻松吃下iPhone 7中 A10处理器的全部订单,把2015年还在代工A9处理器的三星挤出局,一举奠定了台积电的江湖地位。

依靠着InFO,苹果A10处理器在沿用16nm FinFET 工艺的情况下,依旧实现了不俗的性能提升,相较于隔壁用上三星10nm工艺的骁龙835和Exynos 8890也未逊色多少。

而先进封装这把利器,此时借由苹果之手,揭开了它神秘的面纱,向着世人款款而来。

封装,摸着石头过河

苹果与先进封装的故事,可能还得从2007年讲起。

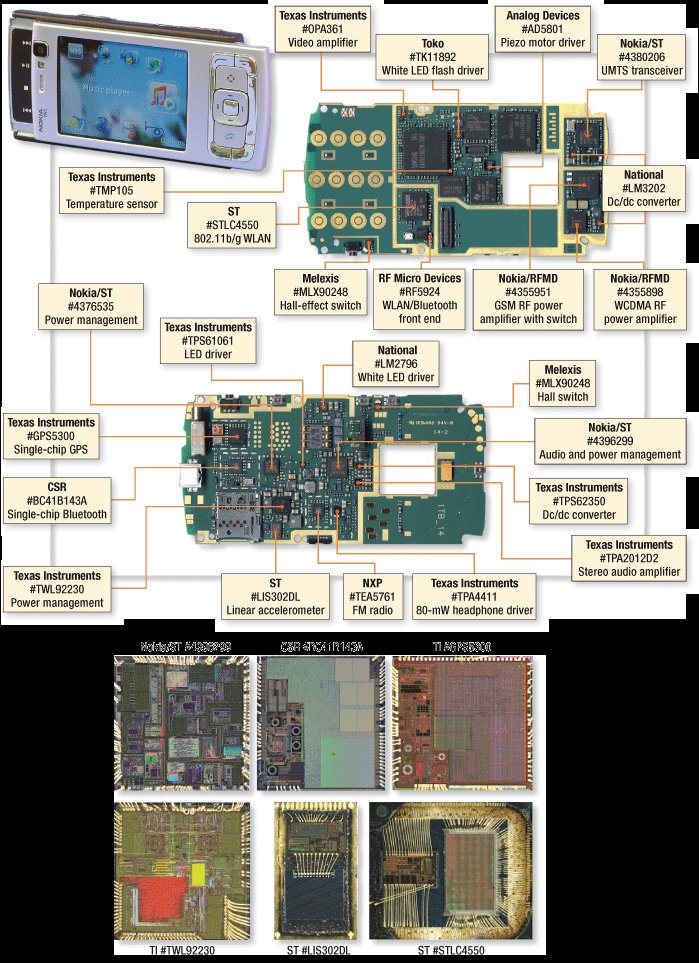

下面这张图是诺基亚N95——一款发售于2007年3月的智能手机的主板,它不仅搭载了强悍的双处理器,还有密密麻麻的模拟芯片,其复杂程度,并不亚于当时任意一款高端笔记本电脑。

同时N95还有三块不同的存储芯片,散布在两颗处理器的周围,光是想要弄清这款手机的硬件架构,就需要花费不少力气,维修起来也是件相当麻烦的事情。

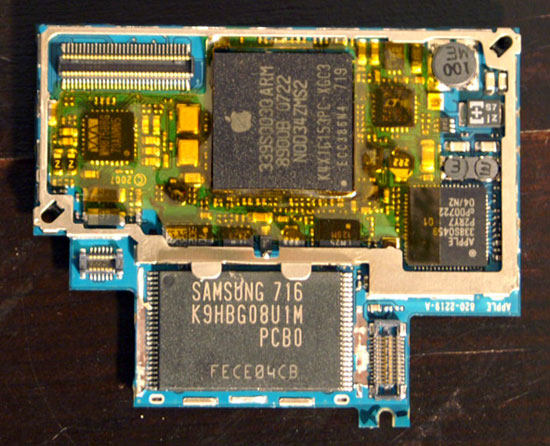

而另外一张主板图同样来自于2007年发售的手机——初代iPhone,仔细观察后,我们会发现,整个主板的集成度相较于N95更高,各类芯片密密麻麻地排布在一起,彼此间的空隙大大缩短。

更重要的是,我们在这个主板上,只能找到处理器与NAND,在所有手机中都能看到的DRAM却没了踪影,难道说苹果有什么黑科技,能把DRAM丢到副板上?

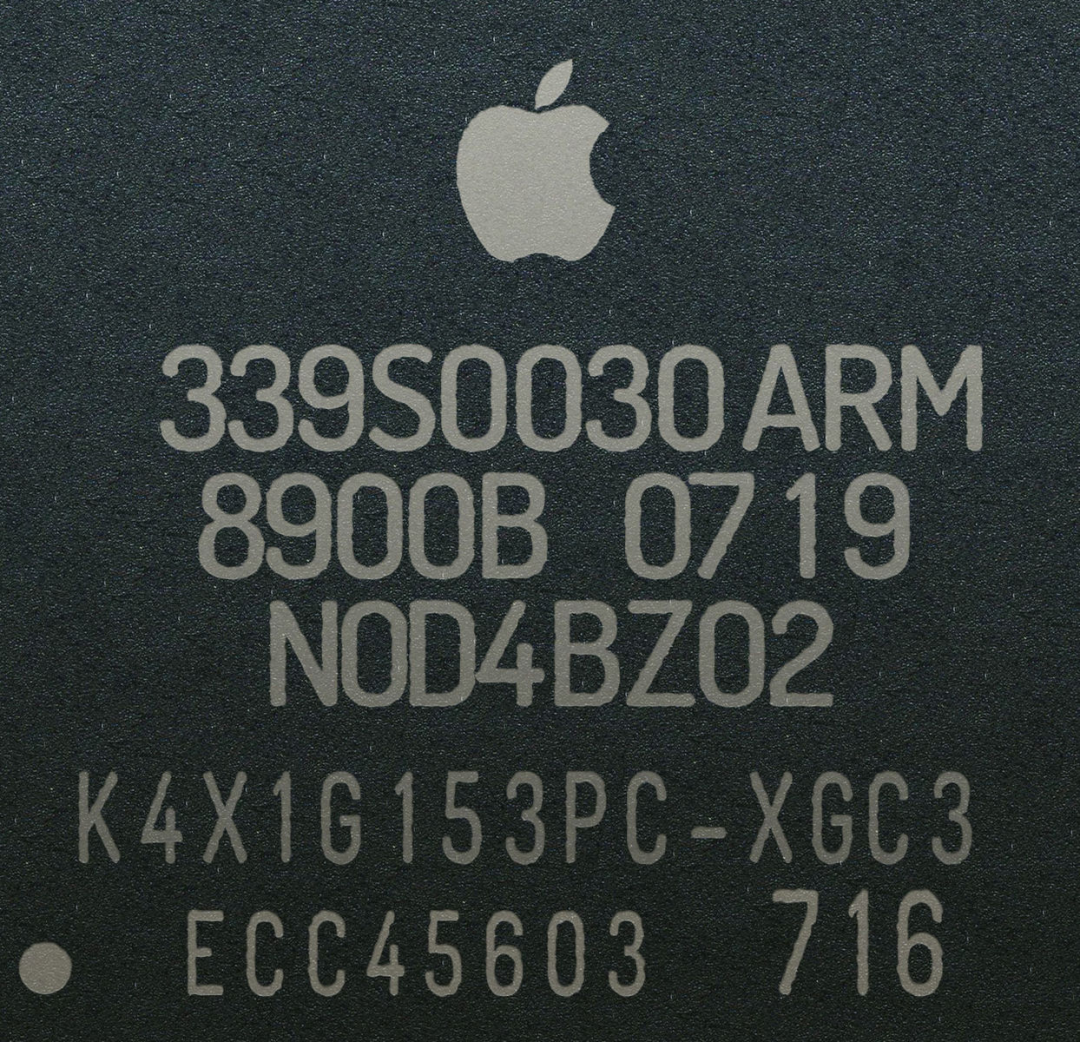

答案藏在苹果Logo芯片的下方,这颗名为APL0098的SoC,实际上是三星S5L8900的换皮版,它的下方,封装堆叠了两块三星出品的512 MB SDRAM,是的没错,苹果在初代iPhone上就采用了层叠式封装 (PoP),将DRAM和SoC集成在了一起。

而这项技术,自然也是出自三星之手,台积电当时也不得不甘拜下风,从初代iPhone到iPhone 5s,所有苹果处理器与封装均由三星单独完成,甚至于苹果A4自研芯片的研发,也在相当程度上受到了三星的影响。

有中国台湾半导体人士评价道,三星是举世唯一可量产存储与处理器,也有自家封测厂的半导体厂,由它承制,整个A7处理器可在「一个屋顶」下完成,在成本、整合度拥有巨大优势,台积电确实难以在短时间内追赶上。

苹果青睐PoP封装也不是没有理由的,与传统封装相比,PoP封装占用较少的基板,而较小的尺寸与较少的重量反过来又减小了电路板面积,而与DRAM较短的互联能实现更快的数据传输速率,且在制造过程的每个环节都能节约成本。

iPhone 5s上的先进封装不过是苹果小试牛刀,苹果真正用好这一利器,还要等到2014年的Apple Watch。

在这一年9月的发布会上,苹果的CEO库克在时隔多年后又一次准备了One More Thing,只不过这次主角是智能穿戴,继iPad之后,苹果又推出了Apple Watch这一全新品类。

发布会上,库克也是大吹特吹了一通,虽然Apple Watch并不是市面上最早的智能手表,但库克仍然把它视作一款革命性的产品,“它不是缩小版的 iPhone,而是一种'直接通过手腕进行通信的创新方式,它的功能远不止这些。"库克在舞台上信誓旦旦。

Apple Watch的诸多先进功能现在看来已经稀疏平常,大部分千元级别的智能手表都可以轻松做到,但它的核心——S1芯片却是其他厂商从未追赶上的。

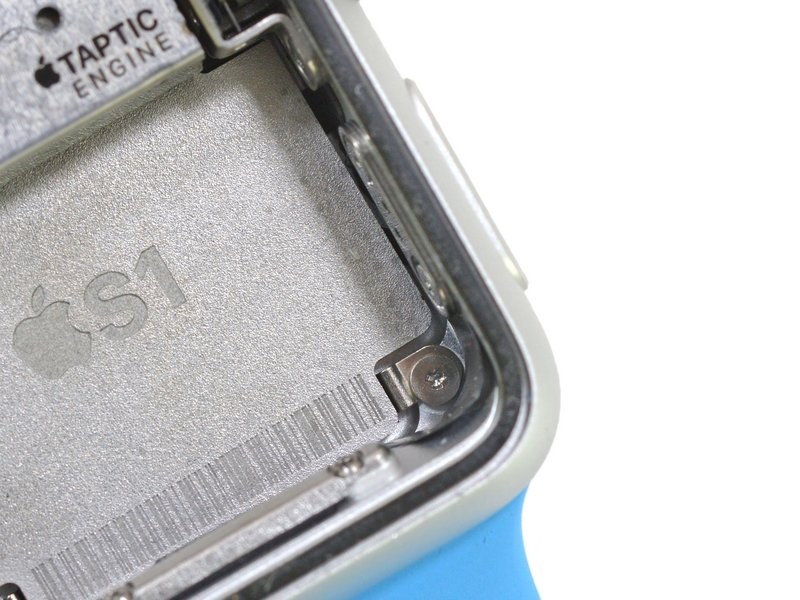

当拆解机构掀开Apple Watch的屏幕时,映入眼帘的只有一块电池和一颗线性振动马达,驱动手表的处理器却没了踪影,直到掀开电池,印着苹果Logo的封装芯片才得以揭晓。

这块印着S1的芯片被牢牢压在了电池和马达下面,而它采用的封装工艺,正是我们今天津津乐道的SiP(System In a Package系统级封装)。

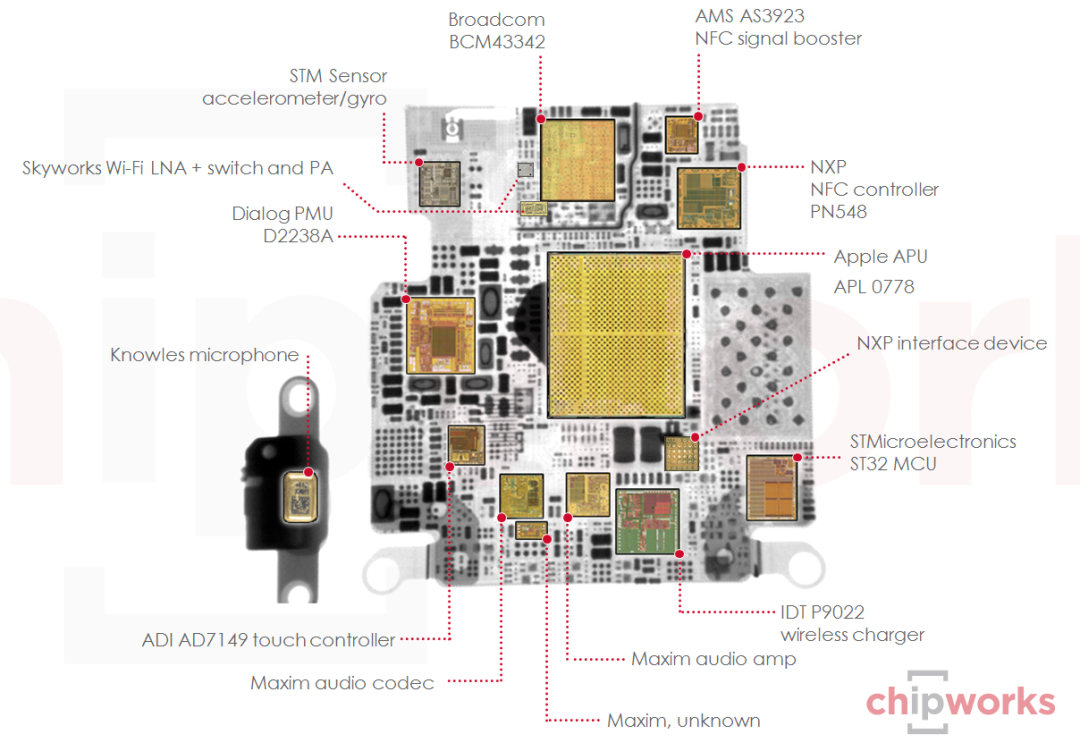

拆解显示,SiP封装真正体现了将整个系统进行封装的精髓,在一块26.15 mm x 28.50 mm的主板上,集成了多达14颗左右的核心芯片产品,以及上百个电阻电容等元器件,所有元器件都有各自独立的封装,并紧密有序地排列在主板上,而除了惯性组合传感器外,其他都元器件都封装在一起,整个封装的厚度仅为1.16mm。

26.15 mm x 28.50 mm×1.16mm,传统芯片的大小,构成了一个系统,其复杂程度,甚至超越了当年与它一同发售的iPhone 6主板。

但先进封装的背后,不再是熟悉的三星操刀,苹果把目光抛向了中国台湾,晶圆代工固然是这里远近闻名的优势,台积电就肩负着代工A8芯片的重任,但封装测试作为半导体中极为重要的一环,中国台湾也并不比其他国家地区逊色多少。

那S1芯片,背后又是谁在出力呢?据媒体报道,S1的 SiP基板出自景硕与南电之手,而SiP封装及模组代工则由封测大厂日月光独占,三大供应商因苹果走到了一起,一同为初代Apple Watch小巧身躯里注入了强大的动力。

PoP加SiP,苹果摸着石头过河,在先进封装上踩出了一条属于自己的路。

强强联合,改变世界

眼看着自初代iPhone以来,先进封装越来越吃香,苹果也开始琢磨起了更高级的封装形式,光是三星的PoP已经难以满足苹果的胃口,更薄的封装已经势在必行。

而代工过A8和部分A9芯片的台积电,拿出了一项苹果无法拒绝的技术——InFO。

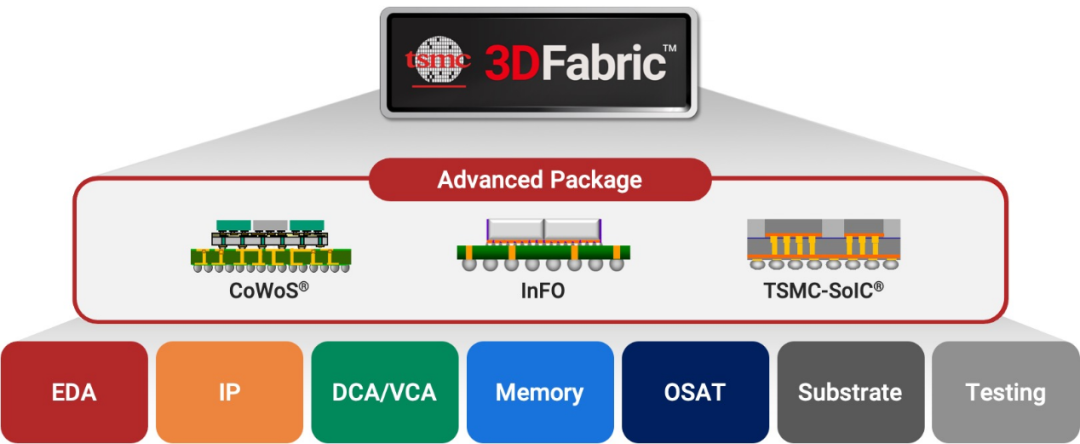

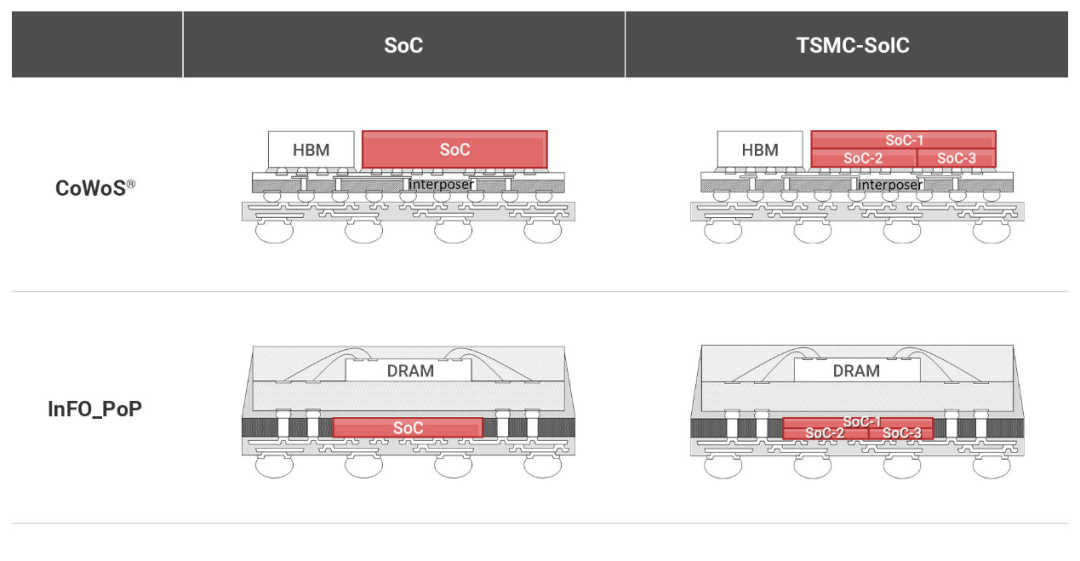

事实上,台积电从2009年就已开始布局封装,其中的带头人是蒋尚义,而负责开发的,就是前文中提到的余振华,他一手缔造了今天在AI中正火热的CoWoS。

当时张忠谋对先进封装这个方向极为看好,还专门拨了400个研发工程师给余振华,他也不负众望,在三年后顺利开发出CoWoS技术,即第一代CoWoS技术。

这项2011年发布的技术,首先是被赛灵思的高端 FPGA 采用。其中Si 中介层的最大尺寸为775mm2 (25 mm x 31 mm),接近一个掩模版的曝光尺寸(26mm x 33mm)(在 ArF 浸入式光刻机的情况下),而FPGA 芯片制造技术是 28 纳米 CMOS 工艺,采用该技术的赛灵思高端FPGA“7V2000T”在“CoWoS_S”中配备了四个FPGA逻辑芯片。

在2014年发布的第二代“CoWoS_S”中,硅中介层扩大到1150mm2,接近1287mm2,这是1.5分划板的曝光面积,在2015年被赛灵思高端FPGA“XCVU440”采用,其采用20 纳米 CMOS 工艺,配备了三块 FPGA 逻辑芯片。

接连两代的CoWoS,都没有翻起太大的风浪,只有赛灵思成为了台积电这项新技术的顾客,这也让开发技术的余振华产生了动摇,“(好像)某人夸下海口,要了大量资源,做了个没什么用的东西,“他在后续的采访中回忆道。

是CoWoS技术还不够好吗?当然不是,理论上利用这项技术的处理器,可以缩减多达70%厚度,对于寸土寸金的半导体来说,这个诱惑不可谓不大。

但打消他们念头的,是CoWoS的成本,有台积电的客户在接洽时表示,这类技术要被接受,价格不能超过每平方毫米1美分,但CoWoS的价格却达到了5倍以上,即使是大公司,难免也会感到肉疼。

为了改变叫好不叫座的局面,台积电的高层决定开发一个每平方毫米1美分的先进封装技术,性能可以比CoWoS略差一些,但是一定要争取到大客户。

这项技术就是首度用在iPhone 7与7Plus的InFO封装,最终成为台积电吃下苹果A10芯片全部订单的关键之所在。

InFO全称为Integrated Fan-Out,意为集成式扇出型封装,重点为集成和扇出型封装。提到InFO封装,首先要先说一下FOWLP(Fan-Out Wafer Level package)封装。传统的WLP在切割前进行封装,虽然减小了封装尺寸,但是使I/O数量受到了限制,为了满足I/O数量增多的需求,FOWLP应运而生。FOWLP使用扇出型技术,通过RDL层,将Die表面的触点扩展到Die的投影面积之外,增加了凸点布置的灵活性以及增多了引脚数量。通常情况下的FOWLP封装的特点为尺寸较小,无基板,塑封封装。InFO封装在某些方面与FOWLP具有相同的特点,而同时又在其上进行了发展。

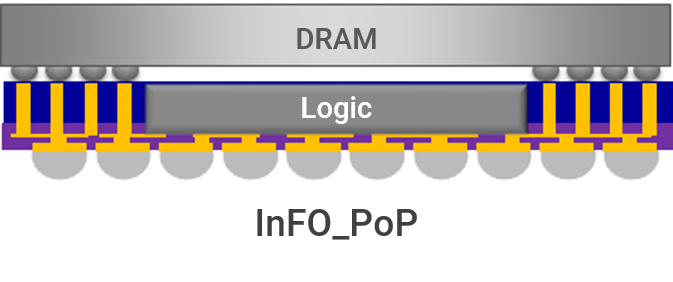

一般而言,Info封装包含三种类型:InFO_oS、InFO_PoP以及InFO_LSI。而台积电给苹果提供的,就是Info_PoP封装,它的全称为Integrated Fan-out Package on Package,是FOWLP与PoP封装的结合体,它将不同类型的芯片在垂直方向上堆叠在一起,下层为FOWLP封装的芯片,上层为 DRAM 等被动芯片,封装之间通过TIV(Through Info Via)进行电气互联。

与三星提供的PoP封装相比,InFO_PoP不需要硅中介层,允许多个倒装芯片组件被放置在封装基板上,通过封装衬底互连到彼此,不仅缩小了芯片面积与厚度,在价格上也更具竞争力,

据一位曾参与苹果订单的封测厂高层主管回忆,三星算是大意失荆州,当台积电提出InFO时,封装经验更丰富的三星,却以为只要将既有的PoP封装稍微改良,就可达到苹果要求的厚度水准,而事实显然并非如此。

而InFO技术几经改良,不仅在iPhone上沿用至今,还让Mac产品也受惠于此。

当苹果在2021年推出 20 核的 M1 Ultra 处理器时,它的 UltraFusion 2.5 TB/s 处理器间互连让世界为之瞩目,而如何做到这一点,也成为了所有半导体行业人士关心的问题。

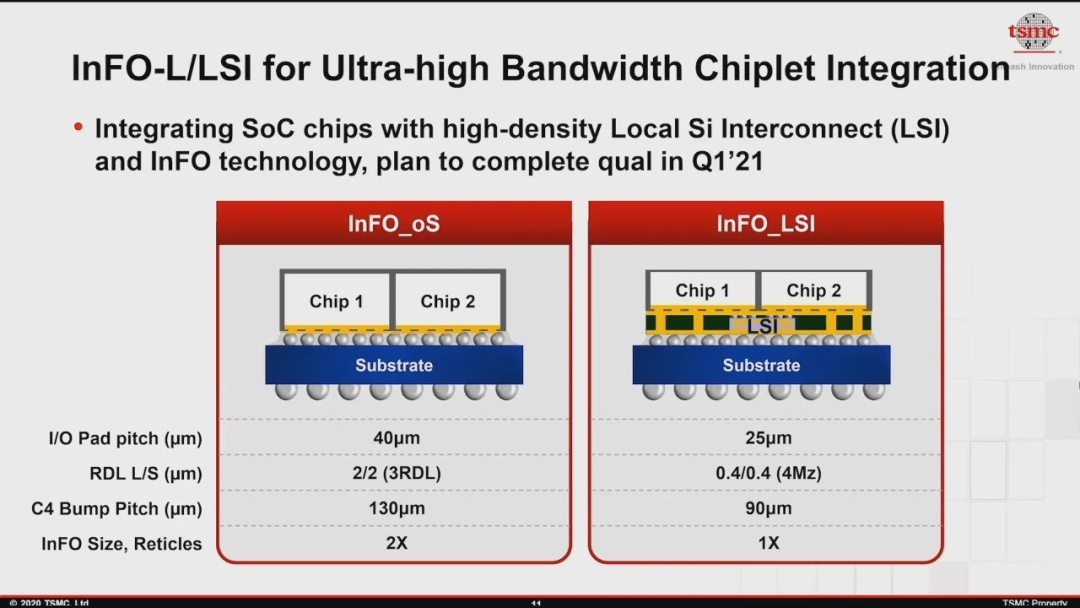

它的背后,就是Info_PoP的迭代版本——Info_LSI技术。

Info_LSI封装全称Integrated Fan-out_Local Silicon Interconnect,此种封装使用硅桥以

及RDL层代替整块硅,达到了性能与成本的平衡,根据TechInsights的解析,硅桥将两块M1 Max处理器连接在一起,实现了低电阻、低延迟和高带宽,而M1 Ultra 也是 TechInsights 记录的第一个使用 InFO-LSI 技术的设备示例。

先进封装不仅把两颗处理器牢牢地粘合在一起,也在苹果和台积电之间搭建起了一座硅桥,两个巨头携手,掀起了一场关于封装的狂风骤雨。

下一块先进封装芯片

对于苹果来说,满足于现有封装技术似乎是完全不可能的事情,即使是在工艺制程上遥遥领先的台积电,也在5nm节点上停留了许久,直到今年才完成了3nm节点的大规模量产,至于更远的GAA和2nm,短期内肯定难以快速实现。

而苹果作为电子消费产品起家的一家公司,对于性能也有种超乎一般公司的执着,每年一迭代手机里的处理器,性能也必须跟着迭代,而新生的自研芯片版Mac,更是需要在英特尔和AMD的压力下,保持住自己领先的性能功耗,而摩尔定律逐渐失效的今天,台积电的先进封装就成为了苹果压箱底的法宝。

据台媒报道,苹果正小量试产最新的3D小芯片堆叠技术SoIC(单线集成电路小轮廓封装),目前规划采用SoIC搭配InFO的封装方案,预计用于MacBook,最快2025~2026年推出产品。

SoIC又是什么新技术呢?根据台积电在第二十四届年度技术研讨会中的说明,SoIC是一种创新的多芯片堆叠技术,是一种晶圆对晶圆(Wafer-on-wafer)的键合(Bonding)技术,这是一种3D IC制程技术,可以让台积电具备直接为客户生产3D IC的能力。

最让人啧啧称奇的是,SoIC技术是采用硅穿孔(TSV)技术,可以达到无凸起的键合结构,可以把很多不同性质的临近芯片整合在一起,当中最关键、最神秘之处,就在于接合的材料,号称是价值高达十亿美元的机密材料,因此能直接透过微小的孔隙沟通多层的芯片,达成在相同的体积增加多倍以上的性能,简言之,可以持续维持摩尔定律的优势。

台积电赴日本参加VLSI技术及电路研讨会发表技术论文时,也针对SoIC技术发表过论文,表示SoIC解决方案将不同尺寸、制程技术及材料的裸晶堆叠在一起。相较于传统使用微凸块的三维积体电路解决方案,台积电的SoIC的凸块密度与速度高出数倍,同时大幅减少功耗。此外,SoIC能够利用台积电的InFO或CoWoS的后端先进封装至技术来整合其他芯片,打造强大的3D×3D系统级解决方案。

有媒体认为,从台积电最初提出的CoWoS技术,到独占苹果代工的InFO技术,下一个让它笑傲于封装行业的,就是SoIC技术。

目前,台积电的SoIC技术已经在竹南六厂(AP6)进入量产,月产能近2000片,预期未来几年将持续翻倍增长,AMD是其首发客户,最新的MI300采用了 SoIC搭配CoWoS封装的方案。

基于成本、设计等因素考虑,苹果大概率会采用SoIC搭配InFO的解决方案,或许在M3 Ultra上就能一睹这项技术的实力。

PoP技术带领iPhone杀入智能手机市场,InFO让苹果自研移动芯片走上崛起之路,而SoIC,会让苹果在桌面端芯片上掀起一场新的封装革命吗?

「资料来源:」

一个「小媳妇部门」为何能让台积电击败三星、独吃苹果?——天下杂志

Apple M1 Ultra Advanced Packaging Innovative packaging architecture using Apple’s UltraFusion.——TechInsights

Apple Watch超强拆解:主板结构及内部传感器工艺深度分析——SITRI

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

本文来自微信公众号“半导体行业观察”(ID:icbank),作者:邵逸琦,36氪经授权发布。

该文观点仅代表作者本人,36氪平台仅提供信息存储空间服务。

Recommend

About Joyk

Aggregate valuable and interesting links.

Joyk means Joy of geeK