台积电上海技术论坛:3DFabric 技术推动HPC创新

source link: https://finance.sina.com.cn/tech/mobile/n/n/2023-06-30/doc-imyysxhv3655237.shtml

Go to the source link to view the article. You can view the picture content, updated content and better typesetting reading experience. If the link is broken, please click the button below to view the snapshot at that time.

台积电上海技术论坛:3DFabric 技术推动HPC创新

新浪数码讯 6月30日上午消息,近日台积电正式在中国上海召开年度技术论坛,

2022年,台积电与其合作伙伴创造了超过 12000 种创新产品,运用近300种不同的台积电技术。台积电持续投资先进逻辑工艺、3DFabric 和特殊制程等技术,在适当的时间提供合适的技术,协助推动客户创新。

目前,随着 AI、5G 和其他先进工艺技术的发展,全球正通过智能边缘网络产生大量的运算工作负载,需要更快、更节能的芯片来满足此需求。台积电预计到2030年,因需求激增,全球半导体市场将达到约1万亿美元规模,其中 高性能计算(HPC)相关应用占 40%、智能手机占 30%、汽车占 15%、物联网占10%。

从2017年到2022年,台积电对特殊工艺技术投资的年复合增长率超过40%。到2026年,台积电预计将特殊工艺产能提升近50%,

随着台积电的工艺技术从10纳米发展至2纳米,台积电能源效率在十年间以15%的年复合增长率高速增长。 因此台积电工艺技术的产能年复合增长率在2019年至2023年间将超过 40%。

2020年开始量产5纳米技术,及之后推出的通过推出N4、 N4P、N4X 和 N5A 等技术,持续强化其5纳米工艺家族。

台积电的3纳米工艺技术也是半导体产业中第一个实现高量产和高良率的工艺技术,官方预计 3 纳米将在移动和 HPC 应用的驱动下快速、顺利地实现产能提升。台积电还推出 N3P 和 N3X 来提升工艺技术价值,在提供额外性能和面积优势的同时,还保持了与N3E的设计规则兼容性,能够最大程 度地实现 IP 复用。

此外,台积电还推出了业界第一个基于3纳米的Auto Early 技术,命名为N3AE。 N3AE提供以N3E为基础的汽车制程设计套件(PDK),

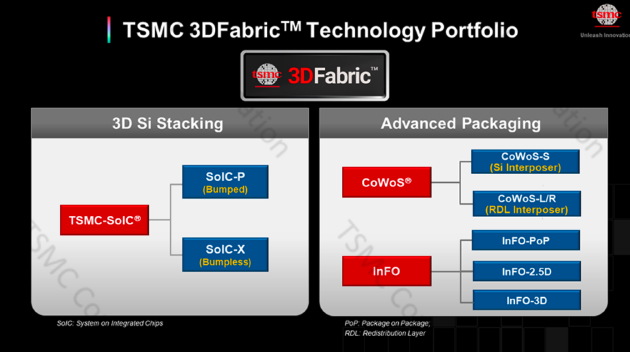

此外,几项相关技术也公布了进展,台积电 3DFabric 系统整合技术包括各种先进的 3D 芯片堆叠和先进封装技术,以支持广泛的下一代产品:在 3D 芯片堆叠方面,台积电在系统整合芯片(TSMC-SoIC)技术家族中 加入微凸块的SoIC-P,以支持更具成本敏感度的应用。

2.5D CoWoS 平台得以实现先进逻辑和高频宽记忆体的整合,适用于人工智能、机器学习和数据中心等 HPC 应用;整合型扇出层叠封装技术(InFO PoP)和 InFO-3D 支持移动应用,InFO-2.5D 则支持 HPC 小芯片整合。基于堆叠芯片技术的系统整合芯片(SoIC)现可被整合于整合型扇出 (InFO)或 CoWoS 封装中,以实现最终系统整合。

CoWoS 家族主要针对需要整合先进逻辑和高带宽存储器的 HPC 应用。根据台积电的说法,已经支持超过 25 个客户的 140 多种 CoWoS 产品。所有 CoWoS 解决方案的中介层面积均在增加,以便整合更多先进芯片和高带宽存储器的堆叠,以满足更高的性能需求。台积电正在开发具有高达 6 个光罩尺寸(约 5,000 平方毫米)重布线层(RDL)中介层的 CoWoS 解决方案,能够容纳 12 个高带宽存储器堆叠。

InFO PoP 自 2016 年开始量产并运用于高端移动设备,可以在更小的封装规格中容纳更大、更厚的系统级芯片(SoC)。在 HPC 应用方面,无基板的 InFO_M 支持高达 500 平方毫米的小芯片整合,适用于对外型尺寸敏感度较高的应用。

3D芯片堆叠技术,SoIC-P 采用 18-25 微米间距微凸块堆叠技术,主要针对如移动、物联网等成本应用。SoIC-X 采用无凸块堆叠技术,主要针对 HPC 应用。其芯片对晶圆堆叠方案具有 4.5 至 9 微米的键合间距,已在台积电的 N7 工艺技术中量产。SoIC 堆叠芯片可以进一步整合到 CoWoS、InFo 或传统倒装芯片封装,运用 于客户的最终产品。

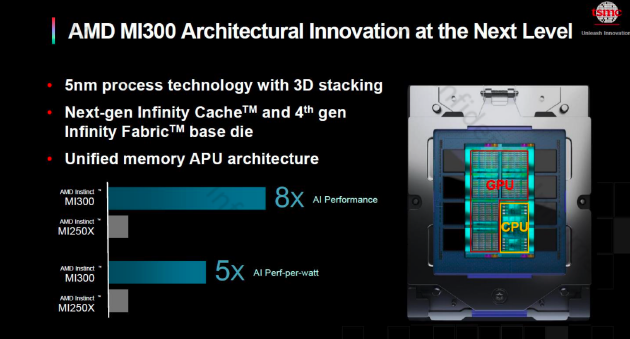

AMD就展示了采用 SoIC-X 技术将 N5 GPU 和 CPU 堆叠于底层芯片,并整合在 CoWoS 封装中,以满足下一代百万兆级(exa-scale)运算的需求,这也是台积电 3DFabric 技术推动 HPC 创新的案例。

在去年的开放创新平台(Open Innovation Platform ,OIP)论坛上,台积电宣布推出新的 3DFabric 联盟,这是继 IP 联盟、电子设计自动化(EDA)联盟、设计中心联盟(DCA)、云端(Cloud)联盟和价值链联盟(VCA)之后的第六个 OIP 联盟,旨在促进下一代 HPC 和移动设计的生态系统合作,

此外,为了满足客户不断增长的需求,台积电加快了晶圆厂建设速度。从 2017 年到 2019 年,平均每年进行大约 2 期的晶圆厂建设工程。加快到2020 年到 2023 年,平均建设进度大幅增加至每年约 5 期的工程。

在过去两年,台积电总共展开了 10 期的晶圆厂新建工程,包括在台湾地区的 5 期晶圆厂工程与 2 期先进封装厂工程,以及全球范围内的 3 期晶圆厂工程。在中国大陆,南京厂新 1 期的 28 纳米制程晶圆厂已于 2022 年开始量产。

Recommend

About Joyk

Aggregate valuable and interesting links.

Joyk means Joy of geeK