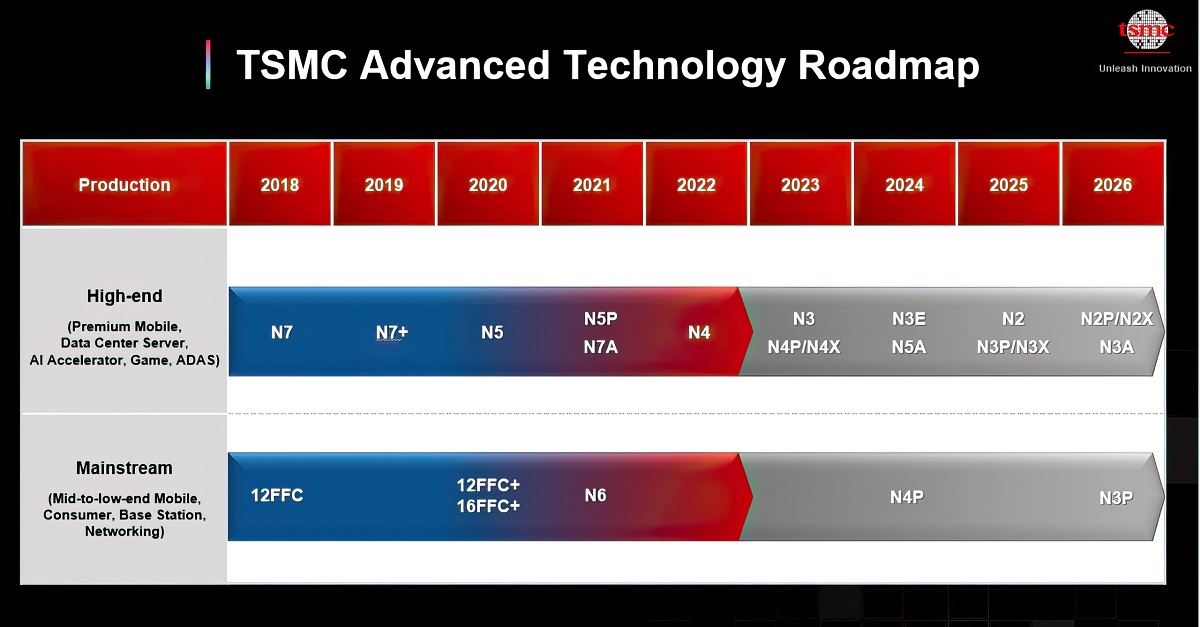

台积电公布2/3nm工艺技术路线图:N3P将于2024H2投产,2025年会带来N2和N3X

source link: http://www.expreview.com/88110.html

Go to the source link to view the article. You can view the picture content, updated content and better typesetting reading experience. If the link is broken, please click the button below to view the snapshot at that time.

台积电公布2/3nm工艺技术路线图:N3P将于2024H2投产,2025年会带来N2和N3X

吕嘉俭发布于 2023-4-30 23:24

本文约 570 字,需 1 分钟阅读

近日,台积电(TSMC)在美国加利福尼亚州圣克拉拉市举办的2023北美技术研讨会上,介绍了先进半导体制造工艺的路线图,包括了3nm和2nm制程节点的各种工艺。

据Wccftech报道,台积电今年将推出改进的N3E工艺,成本更低,有着更好的经济效益,接下来会在3nm制程节点提供更广泛的产品组合,包括N3P、N3X和N3AE,以满足不同客户的多样化需求:

N3P - 一种增强的3nm工艺,计划在2024年下半年投产,在N3E基础上有额外的提升,在相同功率下,速度可提高5%,或者降低5%-10%的功耗,密度为原来的1.04倍。

N3X - 优先考虑HPC应用的性能和最高频率, 与N3P相比,N3X在电压同为1.2V的情况下,速度提高了5%,密度与N3P相同,将于2025年进入量产阶段。

N3AE - 意思是“Auto Early”,将在2023年推出,提供基于N3E的汽车工艺设计套件(PDK),并允许客户在3nm制程节点上推出用于汽车应用的设计,从而在2025年推出完全符合汽车标准的N3A工艺。

目前台积电仍在稳步推进2nm制程节点的技术研发,将采用GAAFET(Gate-All-Around FET)架构晶体管,并在良品率和性能方面取得进展。台积电预计在2025年发布N2工艺,在相同功率下,速度相比N3E提高15%,或者降低30%的功耗,密度为原来的1.15倍。

台积电还在开发N4PRF,推进CMOS射频技术的极限,预计将成为业界最先进的CMOS射频技术,用于数字密集型射频应用,比如Wi-Fi 7射频系统芯片。与2021年推出的N6RF在相同速度下,逻辑密度增加77%,功耗降低45%。

Recommend

About Joyk

Aggregate valuable and interesting links.

Joyk means Joy of geeK