fpga实操训练(vga测试)

source link: https://blog.csdn.net/feixiaoxing/article/details/128429476

Go to the source link to view the article. You can view the picture content, updated content and better typesetting reading experience. If the link is broken, please click the button below to view the snapshot at that time.

【 声明:版权所有,欢迎转载,请勿用于商业用途。 联系信箱:feixiaoxing @163.com】

我自己读书那会,买的电脑还是以台式机居多,平板显示器也是才刚刚流行、且价格较高,视频接口也是以VGA为主。不像现在,基本上视频接口都是以HDMI为主。和HDMI相比较,VGA简单、方便,十分合适用来学习应用。

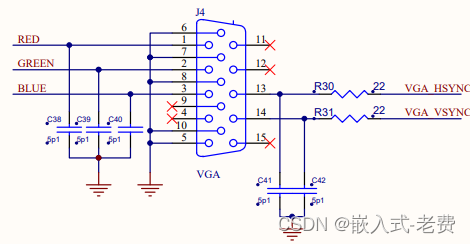

1、VGA接口

开发板上的VGA部分,接口还是非常简单的。虽然接口有15个,但是其中5个是悬空(NC),5个是接地,真正有用的信号其实只有5个。这5个信号分别是红、绿、蓝、行同步、场同步。

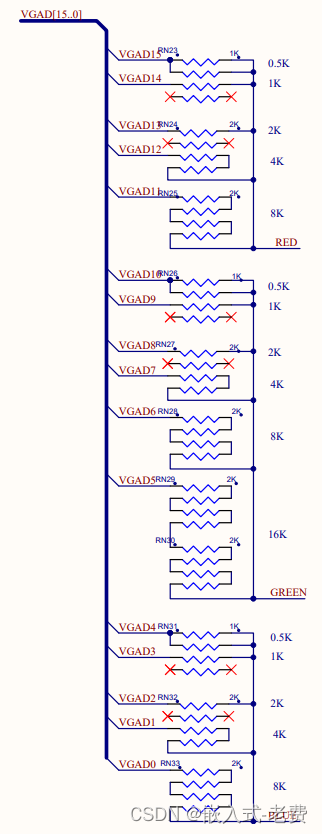

2、FPGA和VGA的连接

FPGA和VGA直接的接口还需要通过上面这一层电路转换,才能输出红、绿、蓝。其中红色有5位,绿色有6位,蓝色有5位,所以可以表现的颜色总共有16位,也就是65536种颜色。0也是一种颜色。

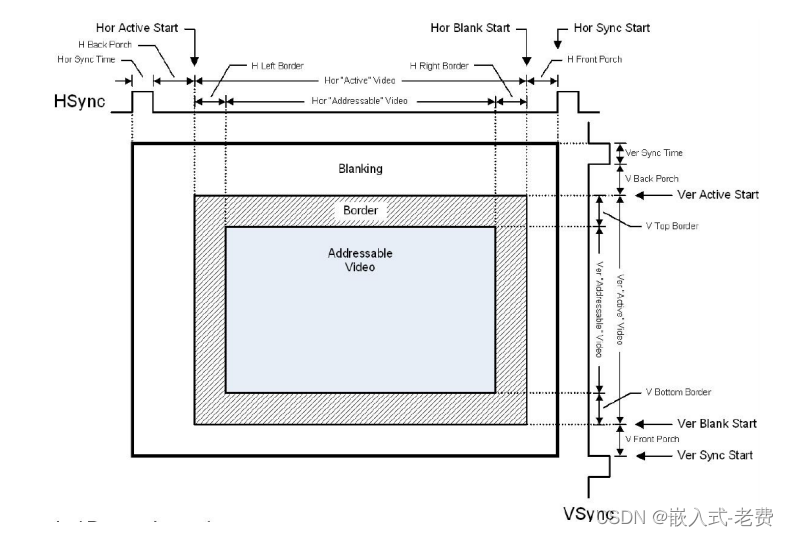

3、VGA的视频时序

VGA视频时序,是我们编写verilog代码的关键。比如说一个1024*768分辨率、60帧每秒的视频流来说,真正VGA处理过的数据是1344*806,这其中还包括了(HSYNC、HBP、HFP,VSYNC、VBP、VFP),这些都是不显示的,所以显示的只是中间一部分内容。整个带宽的话,如果按照1344*806*60来算,大约是65M左右。所以,在fpga实现的过程当中,需要对原来的50M时钟进行倍频处理。

另外需要注意的是,HBP处于前侧,而HFP是处于后侧。同样,VBP处于上方,而VFP处于下方的位置。但是编写verilog的时候,需要从HFP、VFP开始算起,这是比较容易引起疑问的一个地方。

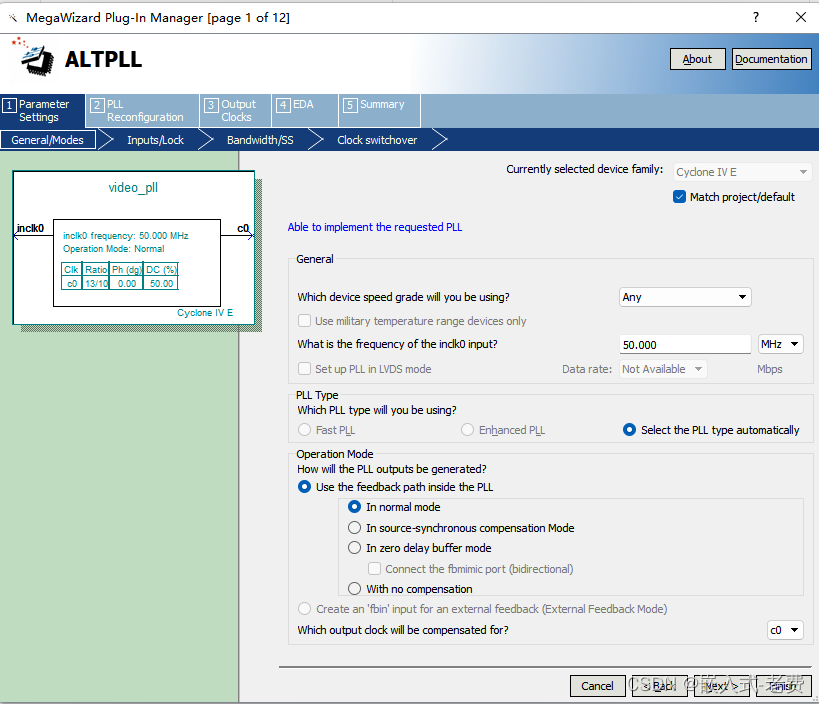

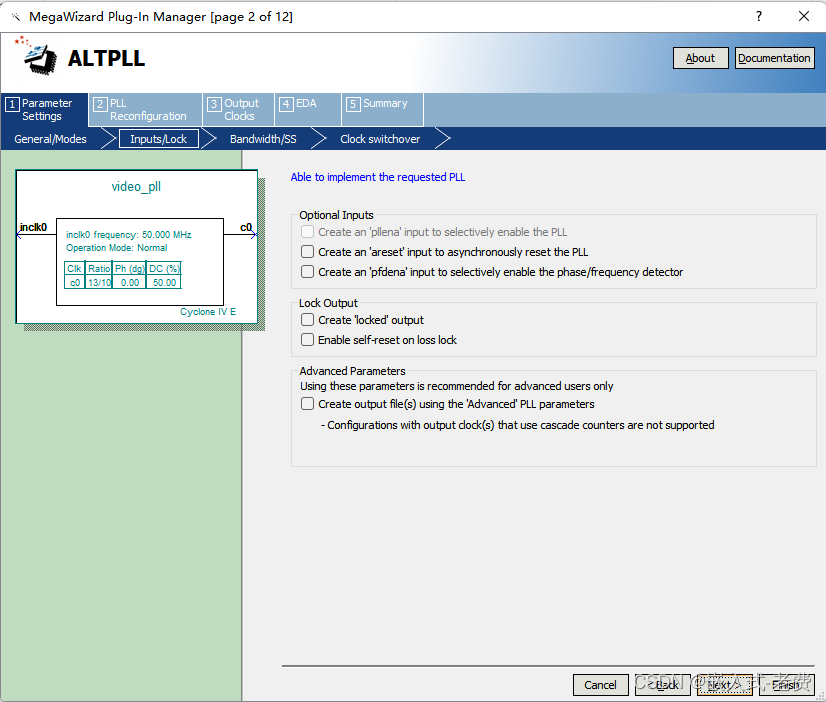

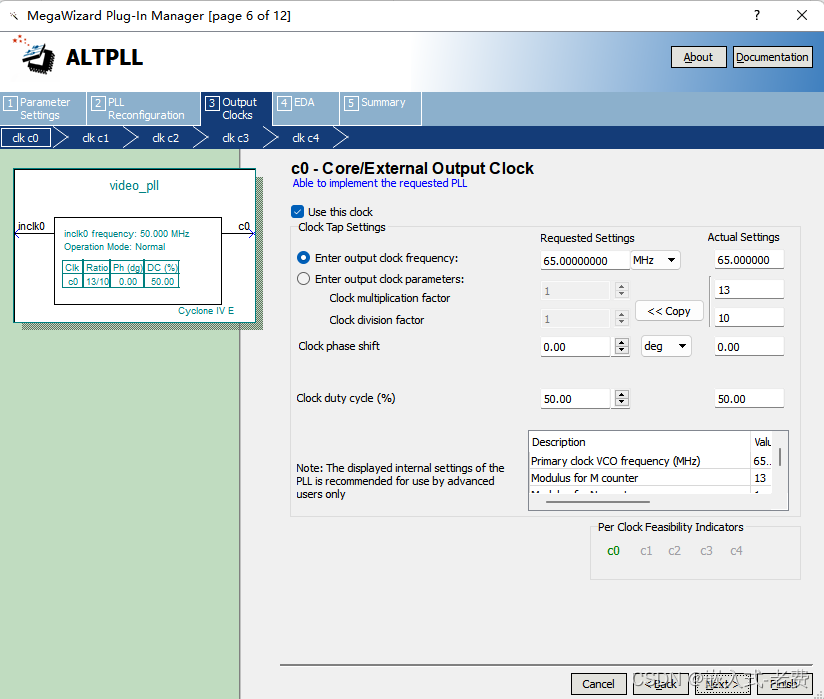

4、准备PLL倍频

倍频之前讨论过。这里只有几个地方需要注意下即可。1)输入时钟为50M,

2)取消复位和lock锁定,

3)只生成一个65M的输出时钟,

5、有了基础的pll,下面可以构建top层代码

top层代码比较简单,这里主要就是实例化video_pll和color_bar两个模块。video_pll刚才已经生成,下面就只需要谈谈color_bar。

6、关于color_bar.v代码

color_bar.v的内容比较多,但是真正有意义的部分还是在于hs_reg、vs_reg、rgb_r_reg、rgb_g_reg、rgb_b_reg的生成。因为它们和最终输出有关。代码中的一大部分内容属于配置部分,因为我们选用的是1024*768,所以相关参数如下所示。video_define.v也只是添加了一行`define VIDEO_1024_768而已。

有了这几行定义,相当于规定了VGA数据的范围。HS_POL和VS_POL代表了起始值。下面就可以看看其他寄存器的含义了。hs_reg_d0、vs_reg_d0主要是为了延迟一拍,因为rgb_r_reg、rgb_g_reg、rgb_b_reg其实也相当于延迟一拍输出的。h_cnt计算一行的数据总数,active_x计算当前行中有效数据索引,v_cnt计算总的行数,hs_reg输出行同步,h_active输出行数据有效,vs_reg输出场同步,v_active输出场数据有效,rgb_r_reg & rgb_g_reg & rgb_b_reg则输出最终的rgb数据。

另外在color_bar.v中,有一个信号de。这主要是为了后续bmp、camera做准备的,本次vga测试其实并没有用到。

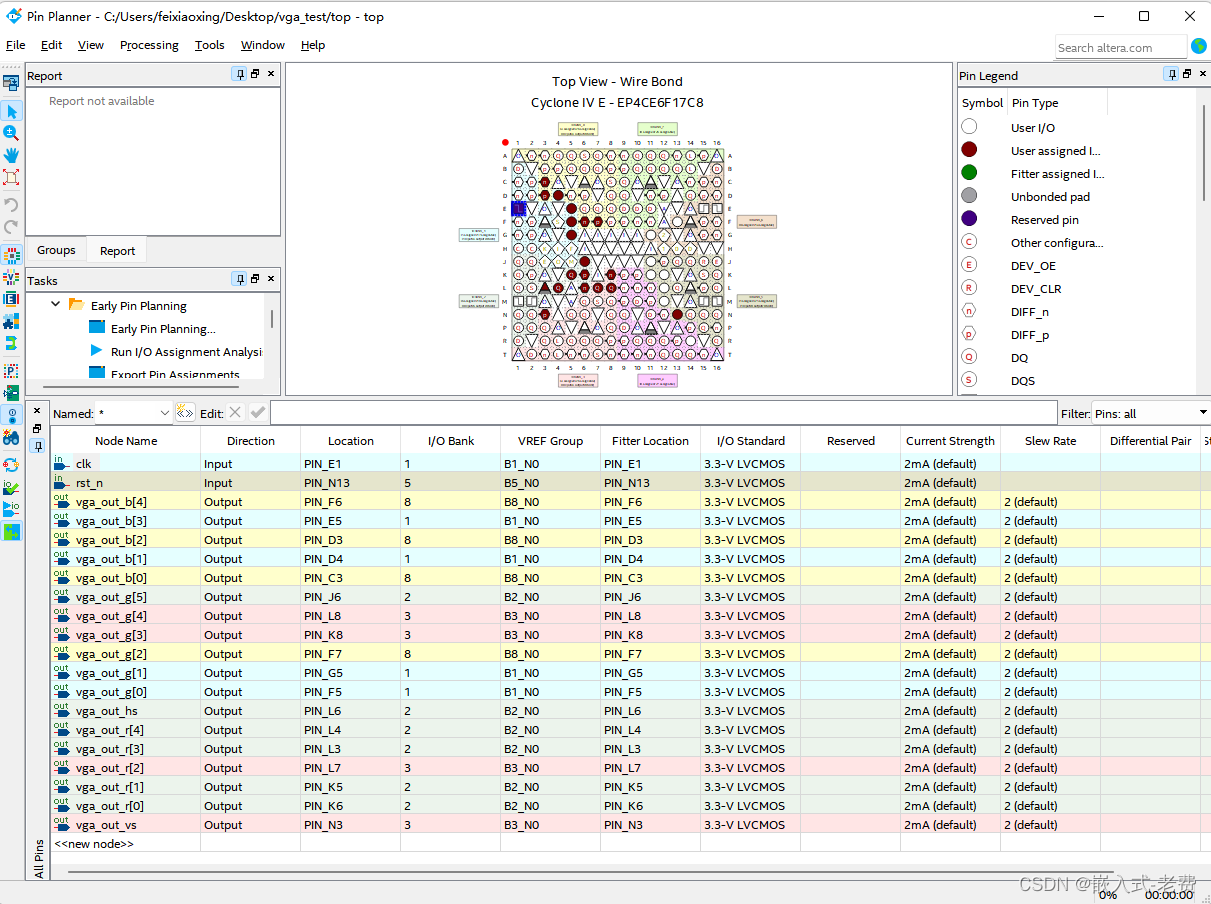

7、pin脚信号的bind

有了video_define.v、vga_test.v、color_bar.v和pll这几个文件,经过编译、综合之后就可以生成对应的sof文件。烧入到fpga开发板之后,不出意外,就可以看到这样的显示效果了,

Recommend

About Joyk

Aggregate valuable and interesting links.

Joyk means Joy of geeK