cpu设计和实现(协处理器cp0)

source link: https://blog.csdn.net/feixiaoxing/article/details/128108394

Go to the source link to view the article. You can view the picture content, updated content and better typesetting reading experience. If the link is broken, please click the button below to view the snapshot at that time.

【 声明:版权所有,欢迎转载,请勿用于商业用途。 联系信箱:feixiaoxing @163.com】

除了通用计算器负责控制和计算之外,cpu如果需要正常有序地运行,还需要一定地协处理器来帮助完成对应地工作。在mips下面,这样地协处理器称之为cp0。协处理器的工作一般包括这几个方面,

1)处理中断和异常;

2)处理mmu和tlb;

3)处理cache;

4)处理其他cpu的相关属性。

之前我们在谈到乘法和除法的时候,涉及到hi和lo这两个寄存器。其实,cp0的处理方法和他们是差不多的。如果是mf读操作,那么这个动作是在exe阶段完成的;如果是写操作,那么这个动作也是在wb阶段完成的。

1、准备cp0_reg.v

2、id添加译码

3、ex阶段

1)增加数据读取操作

看到这里,大家应该对这个代码不陌生了。之前谈到过,所有的寄存器都是在wb之后,才会真正写到寄存器里面的。但是,mfc0的动作是在exe阶段进行的,那么这个时候势必会出现数据读取错误的情况的。所以,解决这个问题最好的办法就是数据预取。id中寄存器预取、ex阶段hi&lo以及mfc预取、mem阶段llbit预取,本质上都是一回事。

2)增加写操作

cp0寄存器的写操作是和通用寄存器分开来的。所以这部分代码需要单独用逻辑快来表达。

4、mem阶段

mem阶段对cp0没有什么影响,主要工作就是把之前ex阶段的数据透传下去即可。

5、准备汇编代码测试

6、将对应的汇编代码翻译成二进制文件

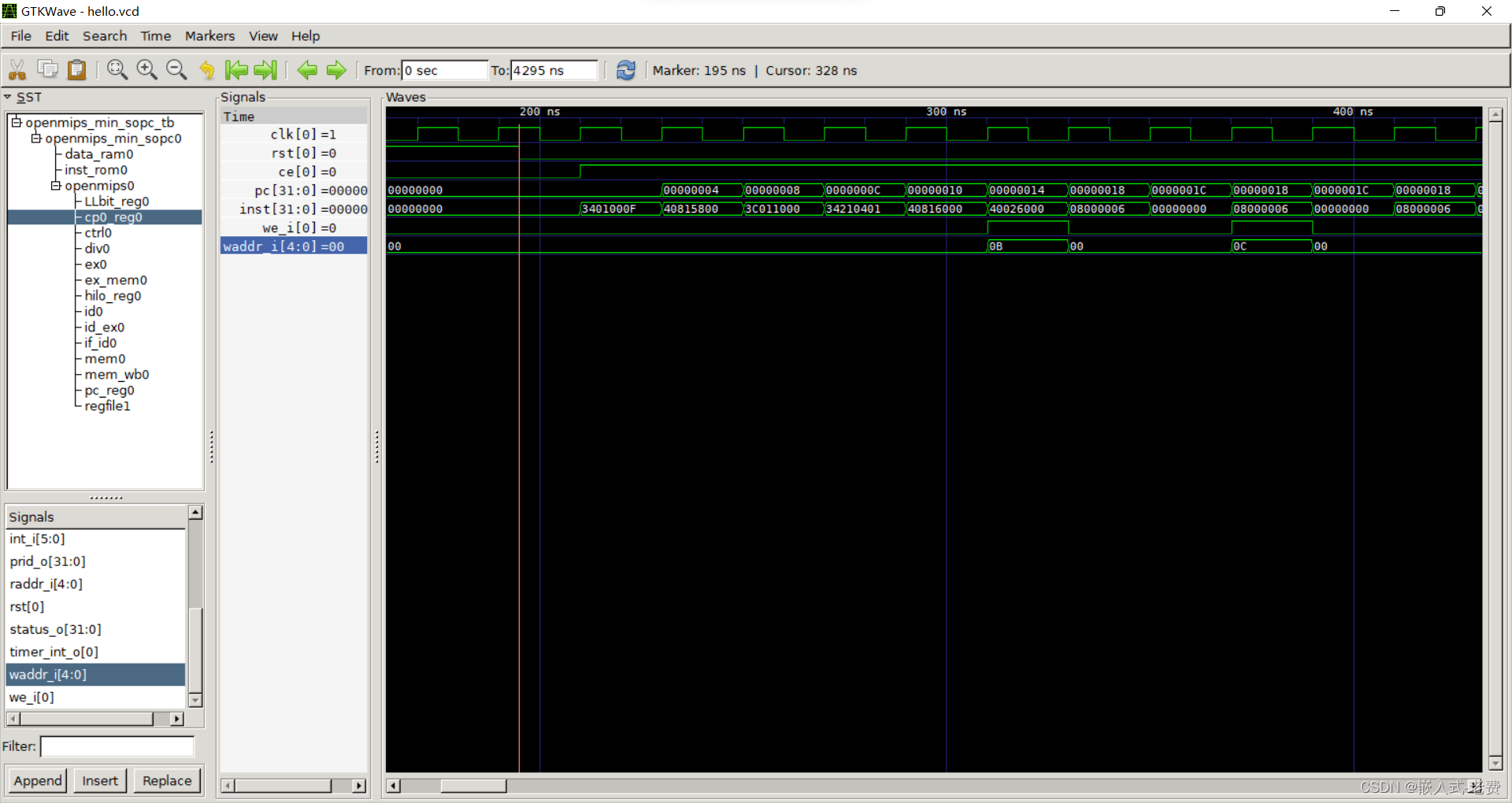

7、利用iverilog和gtkwave进行波形分析

除了通用的pc、inst这些寄存器、wire之外,还可以把cp0_reg0里面的寄存器拉出来看看。重点看看we_i什么时候为高、写入的waddr_i对不对、和之前给出来的汇编代码能不能对的上。最后就是死循环了,因为mips延迟槽的原因,循环肯定是两个pc地址交替进行的。

Recommend

About Joyk

Aggregate valuable and interesting links.

Joyk means Joy of geeK