Rambus推出PCIe 6.0接口子系统,面向下一代高性能数据中心和AI SoC解决方案

source link: https://www.expreview.com/85292.html

Go to the source link to view the article. You can view the picture content, updated content and better typesetting reading experience. If the link is broken, please click the button below to view the snapshot at that time.

Rambus推出PCIe 6.0接口子系统,面向下一代高性能数据中心和AI SoC解决方案

吕嘉俭发布于 2022-10-25 16:13

本文约 530 字,需 1 分钟阅读

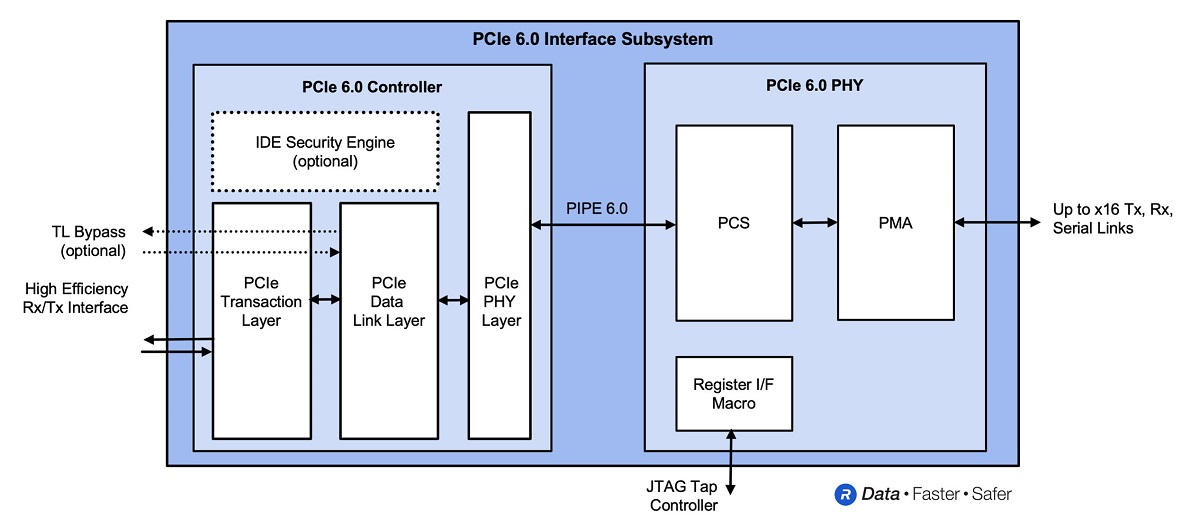

Rambus宣布,推出PCI Express(PCIe 6.0)接口子系统,由PHY和控制器IP组成,同时还支持最新的Compute EXpress Link(CXL)3.0规范,旨在为下一代高性能数据中心和AI SoC解决方案提供支持。

Rambus接口IP总经理Scott Houghton表示,AI、ML和数据密集型工作负载的快速发展正在推动数据中心架构的持续发展,需要更高的性能,而新一代PCIe 6.0接口子系统可以满足下一代数据中心的性能要求,具有一流的延迟、功耗、面积和安全性。

Rambus的PCIe 6.0接口子系统可提供64 GT/s的数据传输速率,经过全面优化后,可以满足高级异构计算架构的需求。在该子系统中,PCIe控制器通过具有完整性和数据加密(IDE)引擎提供最先进的安全性,监控和保护PCIe链路免受物理攻击。

由于Rambus PCIe 6.0接口子系统完全支持CXL 3.0,可实现缓存相干内存共享、扩展和池化的芯片级解决方案。随着CXL变得越来越重要,加上PCIe在数据中心已无处不在,更多的客户会追求不断升级带宽和速度,以支持下一代应用,而访问高性能接口IP解决方案将是实现生态系统的关键。

Rambus PCIe 6.0接口子系统的主要特性包括:

支持PCIe 6.0规范,包括64 GT/s数据传输速率和PAM4信令

支持实现高带宽效率的固定大小的FLIT

实现低延迟前向纠错 (FEC) 以提高链路稳健性

通过IDE引擎实现一流的安全性

向后兼容PCIe 5.0、4.0和3.0/3.1

支持CXL 3.0用于优化内存资源

Recommend

About Joyk

Aggregate valuable and interesting links.

Joyk means Joy of geeK