台积电将在2024年引入High-NA EUV光刻机,或用于2025年2nm芯片生产

source link: https://www.expreview.com/84824.html

Go to the source link to view the article. You can view the picture content, updated content and better typesetting reading experience. If the link is broken, please click the button below to view the snapshot at that time.

台积电将在2024年引入High-NA EUV光刻机,或用于2025年2nm芯片生产

吕嘉俭发布于 2022-9-14 11:34

本文约 580 字,需 1 分钟阅读

台积电(TSMC)的目标是2025年量产其N2工艺,而现阶段主要是其他N3工艺的产量和良品率,这被认为是世界上最先进的芯片制造技术之一。随着英特尔Meteor Lake延期,以及N3工艺的效能未让苹果满意,台积电很可能放弃N3工艺,将重点转移到明年量产的N3E工艺,这属于第二版3nm制程。

虽然台积电短期内的工艺推进计划似乎受到了一些挫折,不过并没有影响其技术的研发,近期台积电负责研发和技术的高级副总裁YJ Mii博士分享了更多的信息。据Wccftech报道,台积电下一阶段将转向具有更大镜头的机器,计划在2024年引入High-NA EUV光刻机,一般认为会用于2nm芯片的制造上。

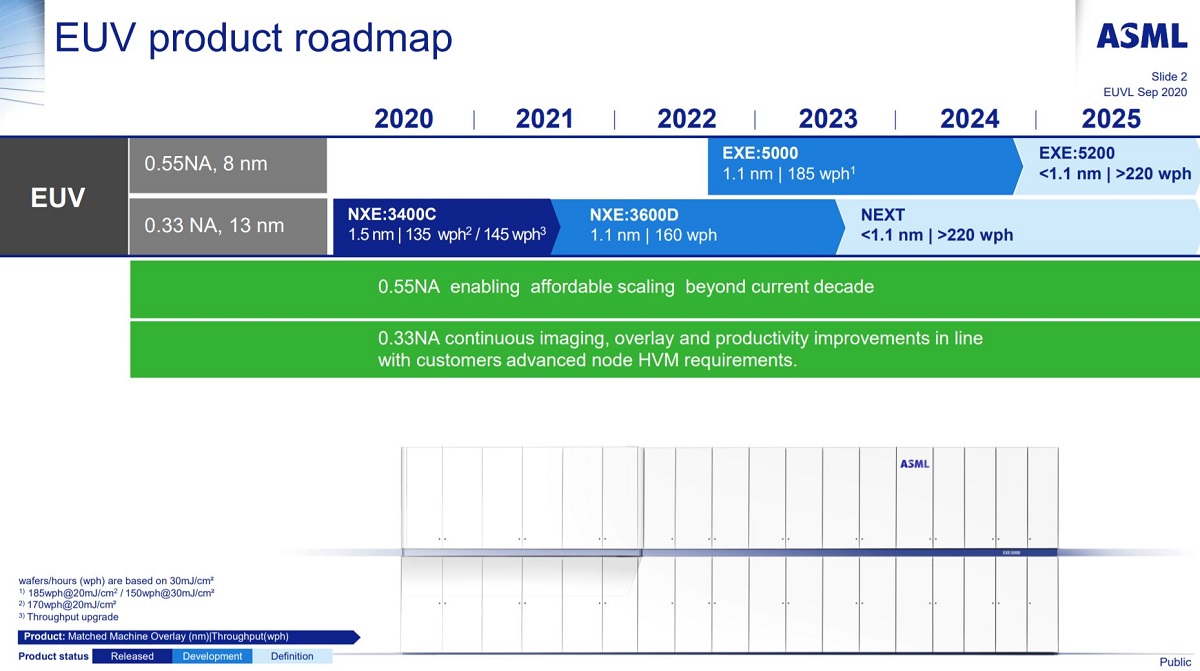

据ASML(阿斯麦)的介绍,具有高数值孔径(High-NA)的新型EUV系统将提供0.55数值孔径,与此前配备0.33数值孔径透镜的EUV系统相比,精度会有所提高,可以实现更高分辨率的图案化,以实现更小的晶体管特征,同时每小时能生产超过200片晶圆。此前英特尔已宣布购买业界首个TWINSCAN EXE:5200系统,计划从2025年使用High-NA EUV进行生产。

台积电在2024年拿到High-NA EUV光刻机后,初期仅用于研发和协作,期间会按照自己的要求进行调整,适当时候再用于大规模生产。与3nm制程节点不同,2nm制程节点将使用Gate-all-around FETs(GAAFET)晶体管,台积电称相比3nm工艺会有10%到15%的性能提升,还可以将功耗降低25%到30%。预计N2工艺于2024年末将做好风险生产的准备,并在2025年末进入大批量生产,客户在2026年就能收到首批芯片。

Recommend

About Joyk

Aggregate valuable and interesting links.

Joyk means Joy of geeK