存储器、I/O组织、微处理器 - 卓亦苇

source link: https://www.cnblogs.com/zhuoblog/p/16324961.html

Go to the source link to view the article. You can view the picture content, updated content and better typesetting reading experience. If the link is broken, please click the button below to view the snapshot at that time.

重点知识

- 存储器的内部结构及访问方法

- 存储器分段以及存储器中的逻辑地址和物理地址

- I/O端口组织及编址方式

- 时序和总线操作以及系统的工作方式和特点。

存储器组织

- 8086有20根地址线,可寻址的存储器空间为1MB,地址范围为0220-1(00000HFFFFFH)。

- 存储器内部按字节进行组织,两个相邻的字节被称为一个“字”;存储数据以字节为单位,将在存储器中顺序存放。

- 若按字存放,一个字的低字节放在低地址,高字节放高地址。并以低地址,做该字地址。

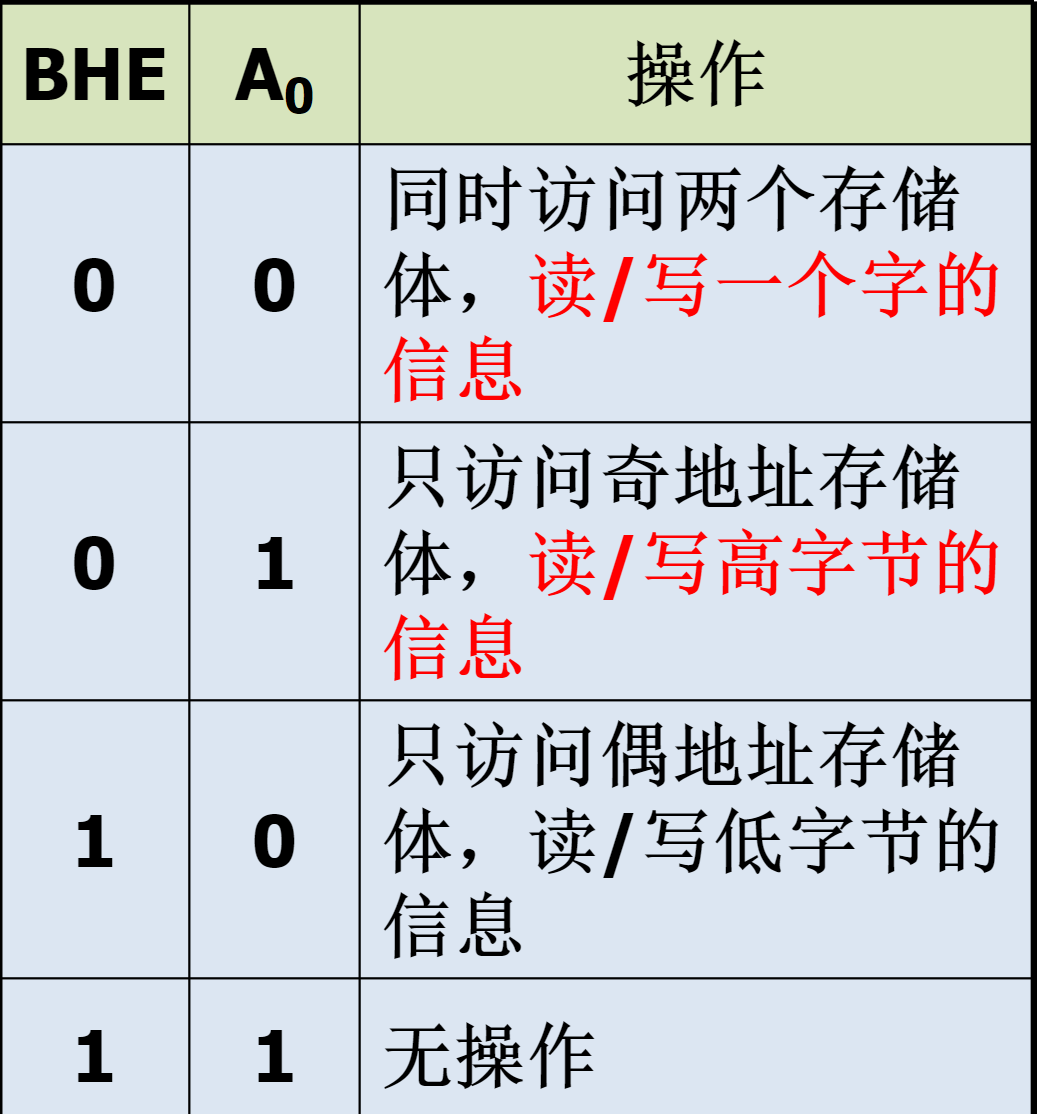

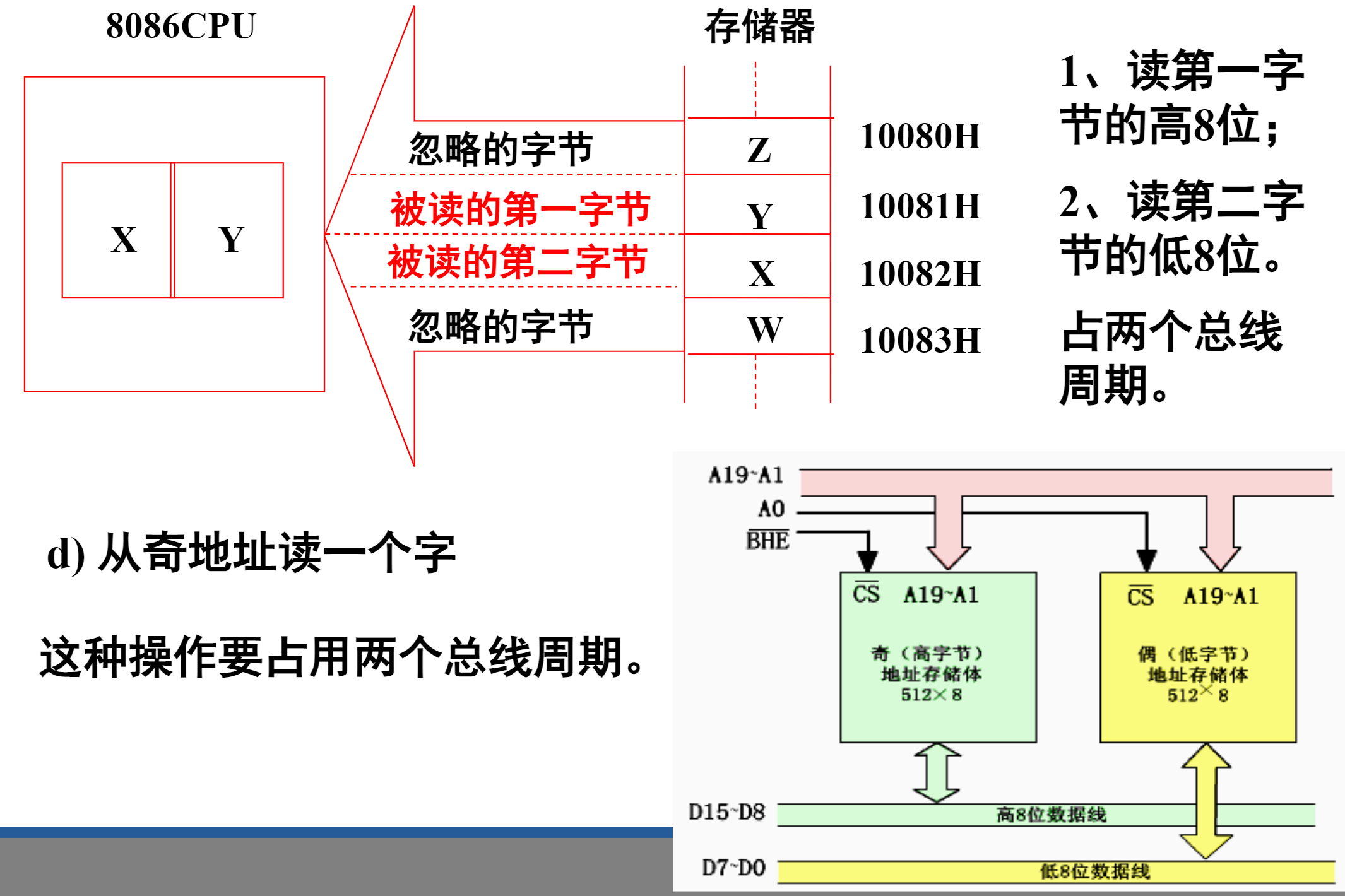

- 若一个字从偶地址开始存放,称规则存放或对准存放,这样存放的字称为规则字或对准字。 对规则字的存取可在一个总线周期完成,非规则字的存取需要两个总线周期。

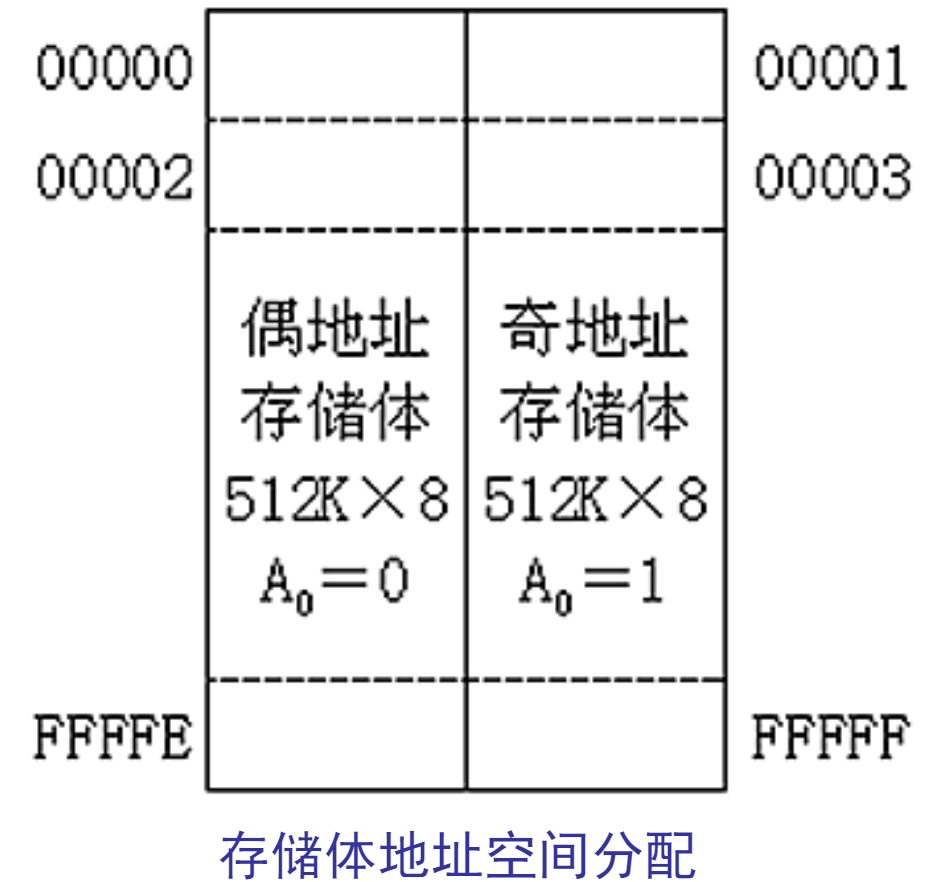

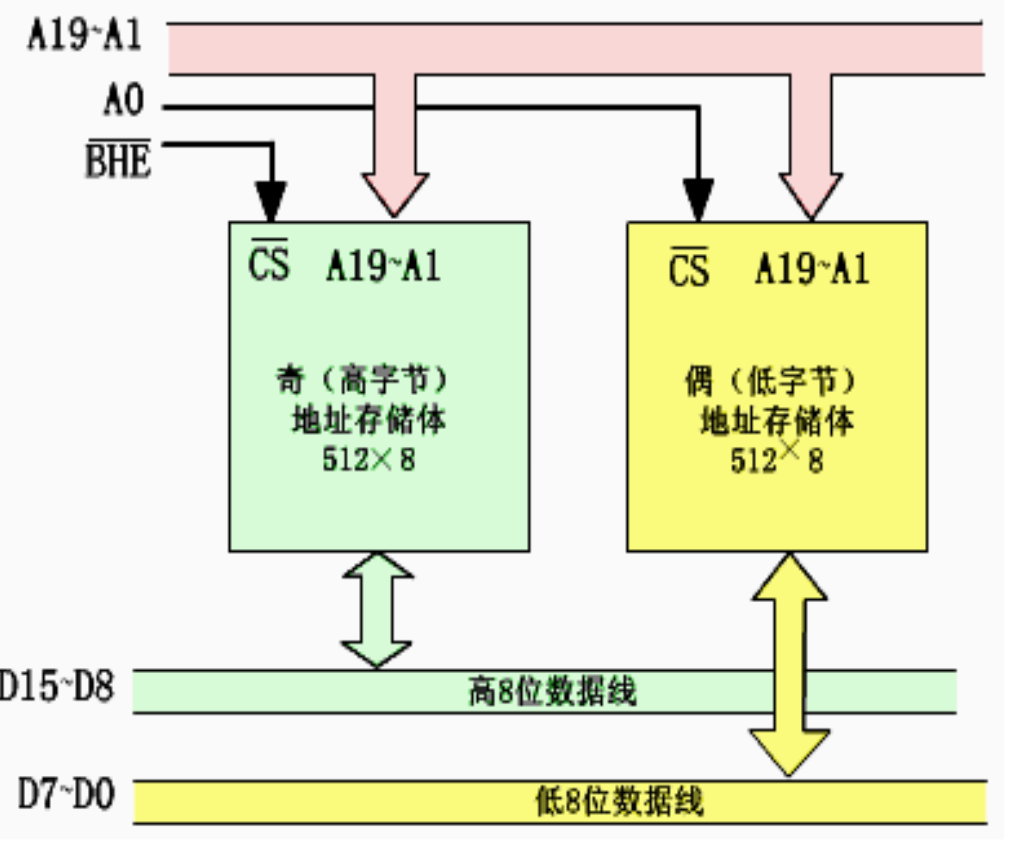

1M字节的存储器,存储空间被分成两个存储体,每个存储体512K字节。 两个存储体之间采用字节交叉编址方式。

与数据总线D15~D8相连的存储体由奇地址单元组成。称高字节存储体或奇地址存储体。 用BHE信号作为选择信号;

存储器分段

- 采用20位地址线来寻址。最大可直接寻址的内存物理地址空间220=1MB 。CPU内寄存器都只有16位,只能寻址64KB(216字节)

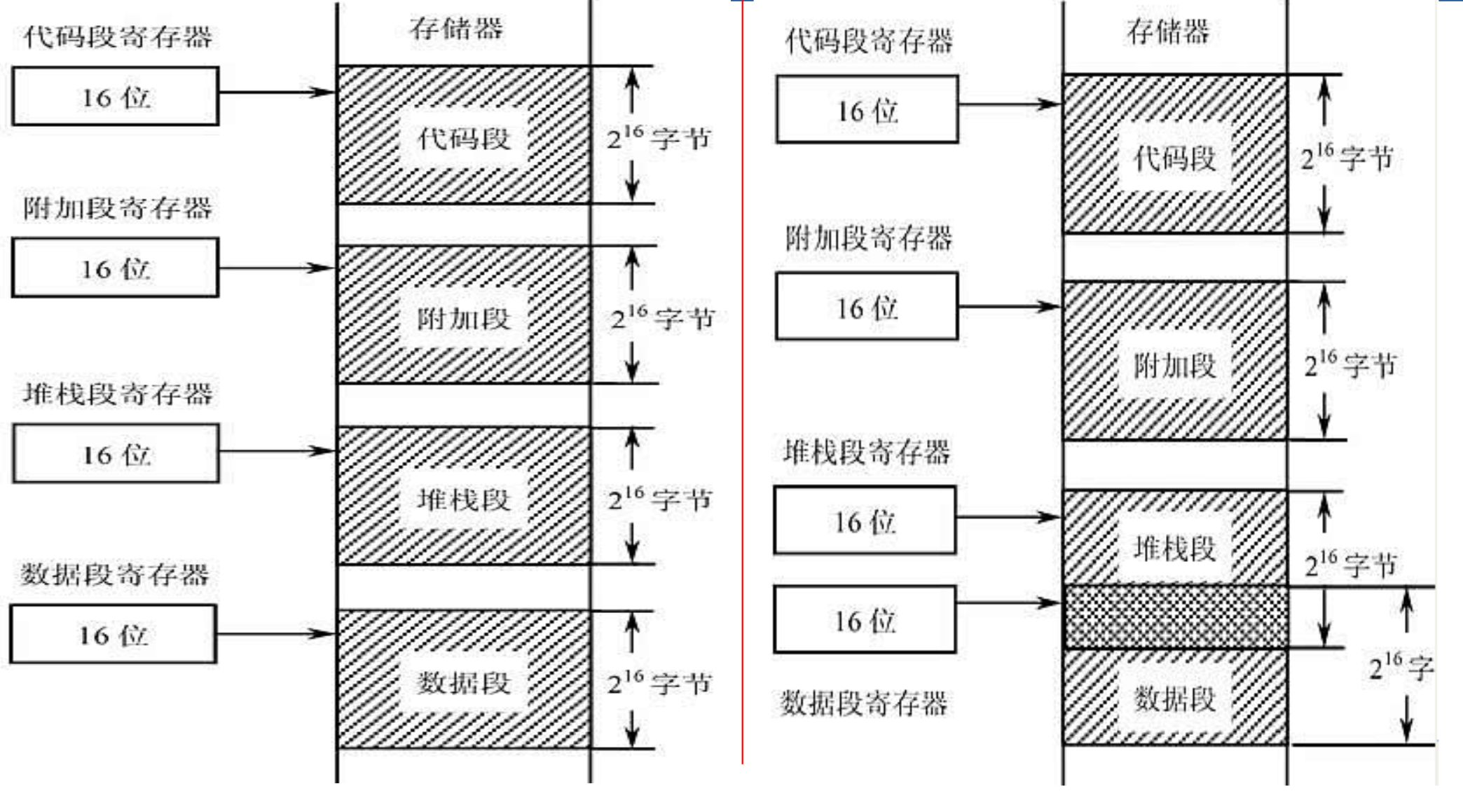

- 把整个存储空间1MB,分成若干逻辑段, 每个逻辑段的容量最大为64KB,可分为16个互不重叠的逻辑段。

- 逻辑段分为代码段、数据段、堆栈段和附加段四种类型;

- 各个逻辑段在整个存储空间中浮动,可相连,可重叠,可分开一段距离。

允许各个逻辑段在整个存储空间浮动,可以相连,也可以重叠,可以分开一段距离

存储器地址

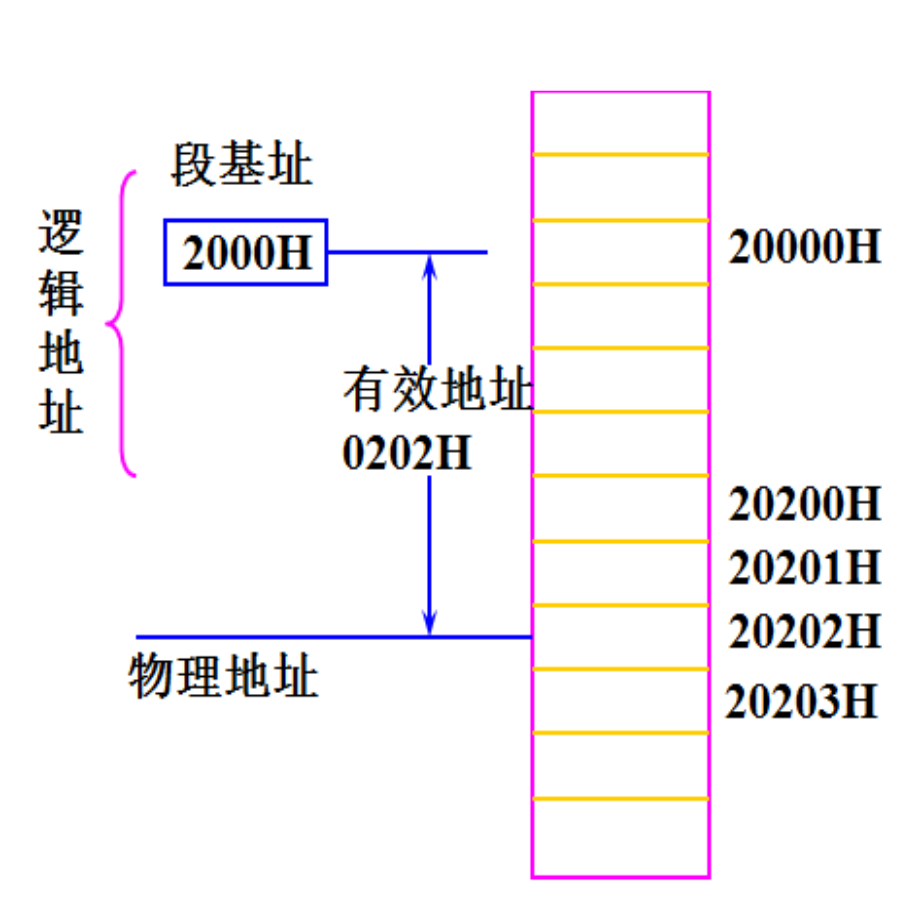

- 段地址:一般存放在段寄存器中(CS、SS、DS和ES)。是指一个段的起始地址,最低4位为零, (2000H)

- 偏移地址(有效地址):要寻址的内存单元距本段段首的偏移量。同一个段内,各个存储单元的段地址是相同的,偏移地址是不同的。(0202H)

- 逻辑地址:在程序中使用的地址,由段地址和偏移地址两部分组成。表示形式为“段地址:偏移地址”。(2000:0202H)

- 物理地址:存储单元的实际地址(20位)。物理地址与存储单元是一一对应关系。(20202H)

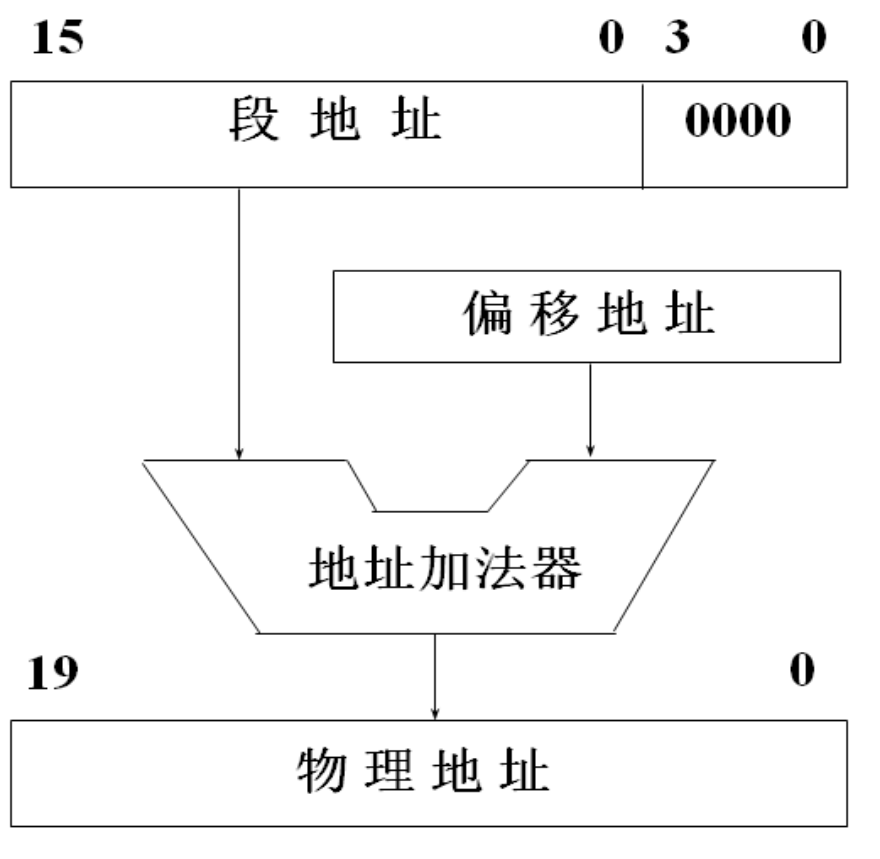

物理地址的计算方法:

物理地址

=段寄存器内容×10H + 偏移地址

=段寄存器内容左移4位+偏移地址

- 取指令物理地址=(CS)×10H+(IP)

- 堆栈操作物理地址=(SS)×10H+(SP)/(BP的表达式)

- 存储器操作数物理地址=(DS)/(ES)×10H+偏移地址

例:内存有由10个字节组成的数据区,起始地址1100H:0020H。计算该数据区在内存的首末单元实际地址。

解:内存数据区逻辑地址1100H:0020H,可知该数据段地址:(DS)=1100H,偏移地址为0020H,对应物理地址:

PA=(DS)×10H+0020H

=1100H×10H+0020H

= 11020H

即该数据区在内存中首单元的物理地址(实际地址)为11020H。

存储空间中10个字节对应10个地址,应占用从起始地址0单元到9号单元的位置,该数据区在内存中末单元物理地址(实际地址):

PA = 11020H+0009H

= 11029H

所以:本题中10个字节组成的数据区,在内存首单元实际地址是11020H,内存末单元实际地址是11029H。

专用和保留的存储器单元

8086系统规定:

1)00000H~003FFH(共1KB):存放中断向量表,中断服务程序的入口地址。每个中断向量占4字节,前2字节存放中断服务程序的入口偏移地址(IP),后2字节存放中断服务程序的入口段地址(CS)。1KB区域可存放256个中断服务入口地址。当系统启动、引导后,这个区域的中断向量就被建立起来。

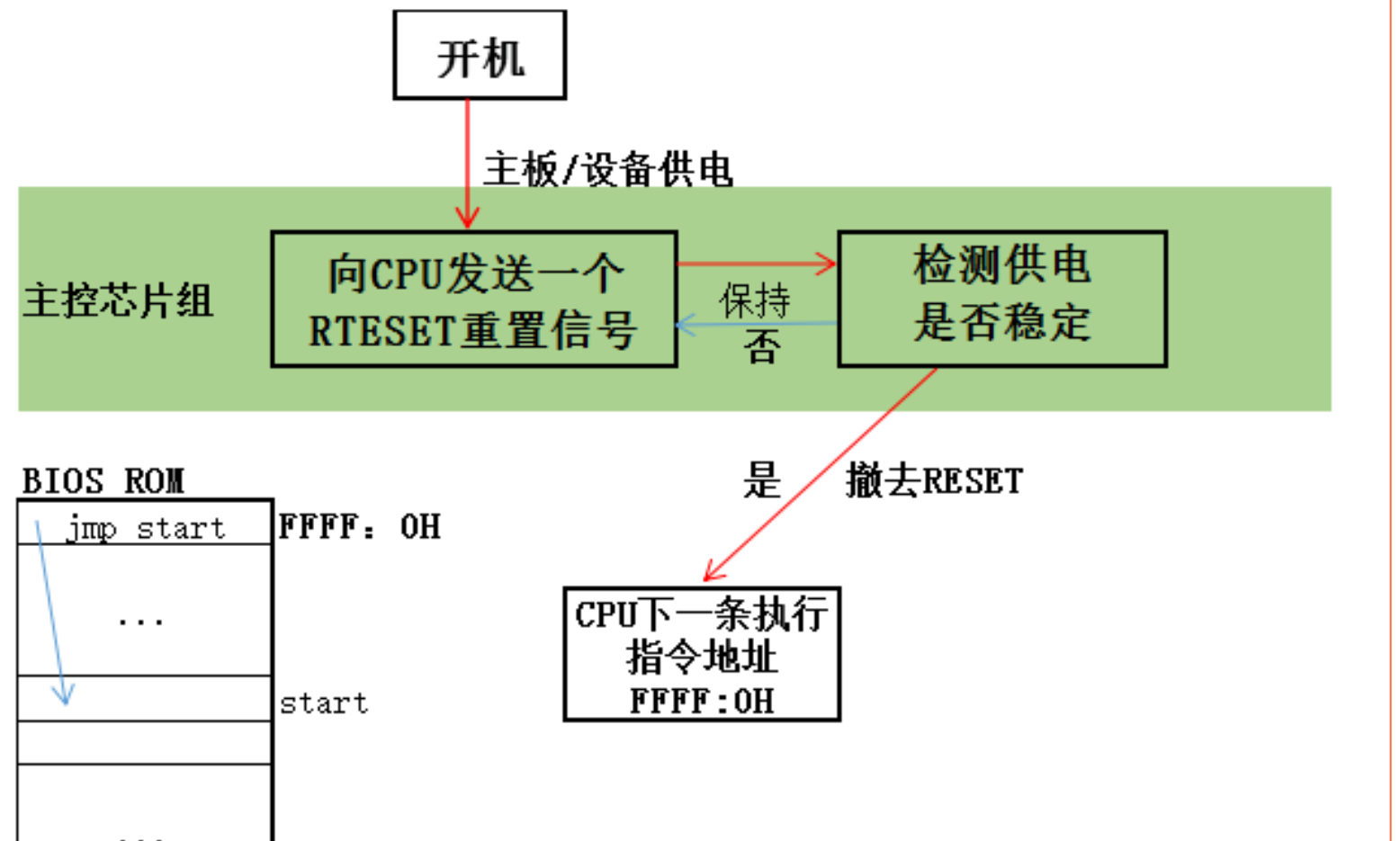

2)FFFF0H~FFFFFH(共16B):存放一条无条件转移指令,使系统在上电或复位时,自动跳转到系统的初始化程序。

系统启动后,CS=0FFFFH,IP=0000H,初始指令的物理地址为0FFFF0H,存放一条无条件转移指令,即转移到系统初始化程序部分。

FFFF:0000H:是BIOS(Basic Input Output System) ROM的起始地址,但不是有效指令开始地址。Jmp指令跳转的START是真正进行BIOS程序起始地址

I/O端口组织

8086微处理器用地址总线的低16位作为对8位I/O端口的寻址线,所以8086可访问的8位I/O端口有216(65536)个。两个编号相邻的8位端口可以组成一个16位的端口。一个8位的I/O设备可以连接在数据总线的高8位,也可连接低8位。

1、统一编址: 把I/O端口看作存储器单元,每个端口占用一个存储单元的地址。CPU访问存储器的指令和各种寻址方式都可用于寻址I/O端口。

2、独立编址: 端口单独编址构成一个I/O空间,不占用存储器地址。有专门输入/输出指令(IN和OUT)。使用16条地址线A15~A0来访问I/O端口,可访问最多64K容量的8位端口或32K容量的16位端口。

8086CPU的操作是在时钟CLK统一控制下进行的。 8086CPU由外部的一片8284A时钟信号发生器提供主频为5MHz的时钟信号。

- 8284A能产生8086所需的系统时钟信号,即系统主频。

- 8284A还可对外界输入准备就绪信号RDY和RES进行同步操作。

- 输出READY信号作为8086的就绪信号READY;输出RESET信号作为8086的复位信号RESET。

8086CPU的总线周期和工作方式

8086CPU经外部总线对存储器或I/O端口进行一次信息的输入或输出过程,称为总线操作,执行该操作所需要的时间,称为总线周期。

1个总线周期,包含4个T时态。T1,T2,T3,T4。

不同的总线操作需要不同的总线信号,对这些信号的变化进行时间顺序的描述称为“总线时序”。

CPU的操作是在时钟统一控制下进行。描述总线操作的微处理器时序有三级

指令周期 → 总线周期 → 时钟周期

- 指令周期:计算机完成对一条指令的读取并执行所需的时间。

- 总线周期:CPU经外部总线对存储器或I/O端口进行一次信息的输入或输出过程所需要的时间。

- 时钟周期 T: CPU的基本时间计量单位,由主频决定。

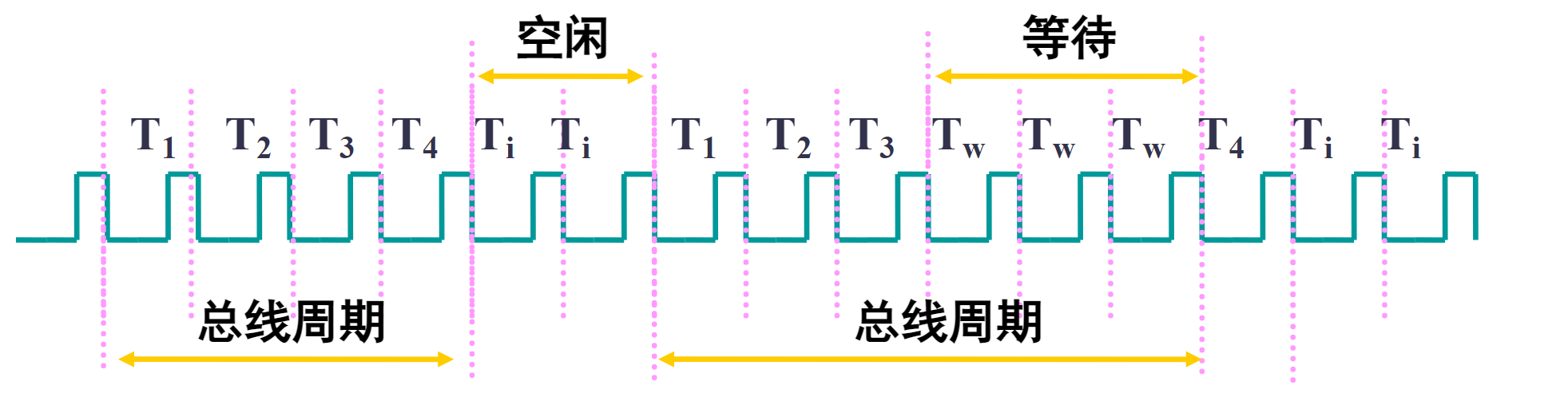

- 等待周期TW:当慢速的存储器或I/O接口,无法在3个时钟周期内完成数据读写操作时,在总线周期中插入等待周期。

- 空闲周期 TI:是指在二个总线周期之间的时间间隔(总线处在空闲状态)。无总线操作时进入空闲周期。

8086CPU由外部的一片8284A时钟信号发生器提供主频为5MHz的时钟信号。

- 基本总线周期:由4个T状态组成:T1、T2、T3、T4。

- 等待时钟周期Tw:在总线周期的T3和T4之间插入。

- 空闲时钟周期Ti:在两个总线周期之间插入。

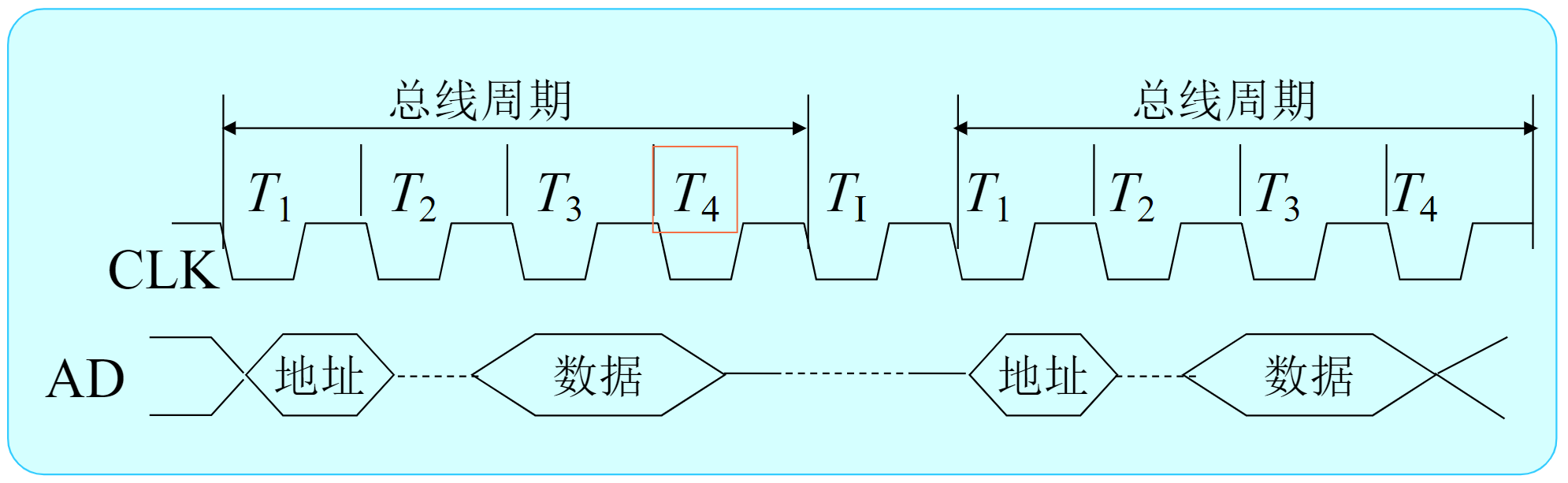

8086CPU采用总线复用操作方式,16位数据总线和地址总线的低16位是共用的,典型的总线周期如图

在没有插入等待时钟周期TW的情况下,总线周期由4个时钟周期组成,即图中T1、T2、T3、T4

- 在T1期间:CPU把存储器或外设的地址放到总线上。

- T2期间:分时复用的地址/数据总线处于高阻态,以便为读入或写出数据作准备。

- 在T3和T4期间:读或写的数据出现在总线上,以使完成读或写的操作。

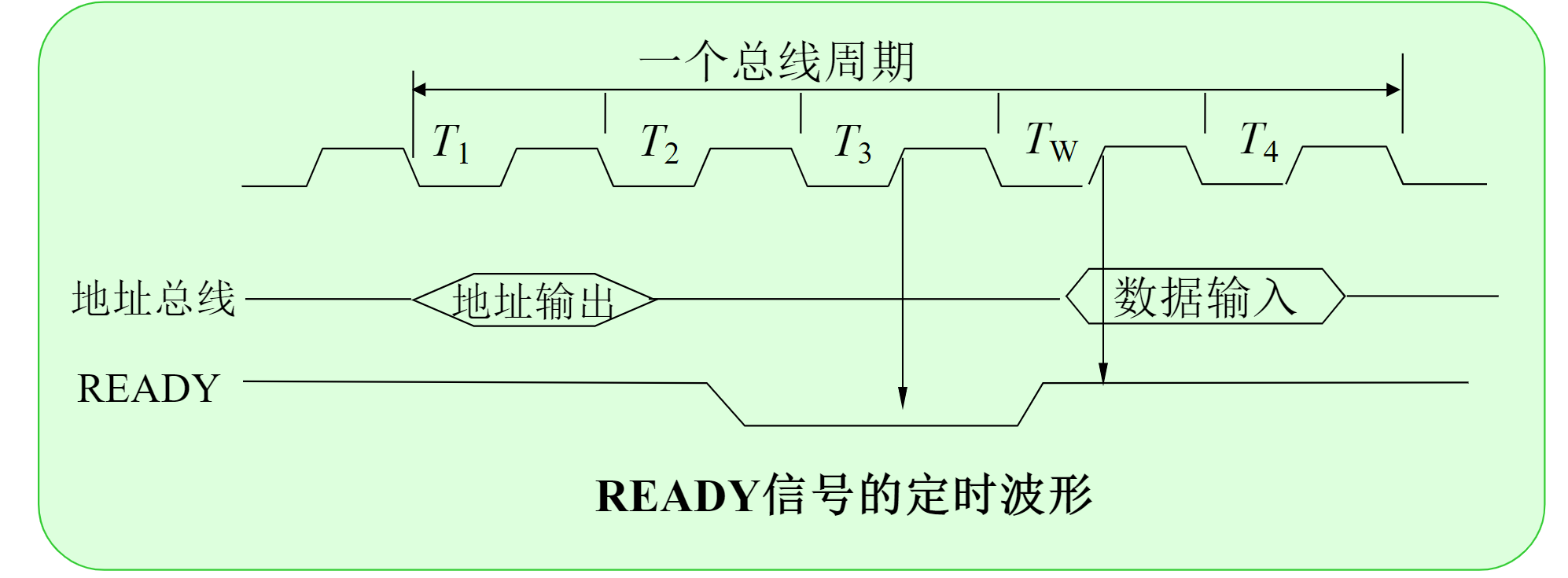

等待周期TW:

如果在T3周期结束之前,存储器或外设未准备好数据传送,就要输入CPU的READY线使之变低电平,从而在T3和T4之间插入一个或多个TW等待周期,直到READY变高,转入T4周期,完成读写操作。

- 任何指令的取指阶段都需要存储器读总线周期,读取的内容是指令代码

- 任何一条以存储单元为源操作数的指令都将引起存储器读总线周期,任何一条以存储单元为目的操作数的指令都将引起存储器写总线周期

- 只有执行IN指令才出现I/O读总线周期,执行OUT指令才出现I/O写总线周期

- CPU响应可屏蔽中断时生成中断响应总线周期

为了适应各种场合的要求,8086CPU在设计中提供了两种工作模式,即最小模式和最大模式。

通过CPU的第33条引脚 MN/MX 来控制。

(1)最小工作模式(MN/MX =1):适用于单微处理器组成的小系统,系统中通常只有一个微处理器,所有的总线控制信号都直接由8086CPU产生,系统中的总线控制逻辑电路被减到最少。

(2)最大工作模式(MN/MX=0):此时,系统中存在两个或两个以上的微处理器,其中有一个主处理器8086,其他处理器称为协处理器。

举例:8086最小模式基本时序

- 总线读周期 8086CPU进行存储器或I/O端口读操作时,总线进入读周期;

- 总线写周期 8086CPU进行存储器或I/O接口写操作时,总线进入写周期。

- 中断响应周期 当8086的INTR引脚上有高电平信号,且中断标志IF=1时,8086CPU在执行完当前指令后,进入中断响应周期。响应中断时CPU将执行两个中断响应周期。

- 总线响应周期 当系统中有其它的总线主设备请求总线控制时, CPU进入总线响应周期。

- 系统复位周期 8086CPU的RESET引脚,可以用来启动或再启动系统

8086在最大与最小模式下的主要区别是增加了一个8288总线控制器。8288接受8086CPU的状态信号S2、S1和S0,经过变换和组合,由8288发出对存储器和I/O端口的读/写信号,对锁存器8282及对总线收发器8286的控制信号。

32位微处理器

80386的主要特点

- 80386微处理器拥有32位数据总线和32位地址总线,可直接寻址4GB(232)的物理存储空间,同时具有虚拟存储的能力,虚拟存储空间达64TB。存储器采用分段结构,一个段最大可为4G字节。

- 系统采用了流水线和指令重叠技术、虚拟存储技术、片内存储器管理技术、存储器管理分段分页保护技术等,使80386系统实现了多用户多任务操作,功能得到大大加强。

- 提供32位的指令,可支持8位、16位、32位的数据类型,具有8个通用的32位寄存器,具有片内地址转换的高速缓冲存储器Cache。

- 提供32位外部总线接口,最大数据传输速率为32Mbps。系统可同高速的DRAM芯片接口,支持动态总线宽度控制,能动态地切换32位/16位数据总线。

- 具有片内集成的存储器管理部件MMU,可支持虚拟存储和特权保护,可选择片内分页单元。片内具有多任务机构,能快速完成任务的切换。

- 通过配置浮点协处理器80387实现数据高速处理,加快了浮点运算速度。

- 80386系统能在时钟频率为12.5 MHz或16 MHz下可靠工作,指令的执行速度可达3~4MIPS以上。

80486的主要特性

- 80486是在复杂指令集计算机CISC技术的基础上,首次采用了精简指令集计算机RISC技术的80X86系列微处理器。

- 把浮点运算部件和高速缓冲存储器Cache集成在芯片内,使运算速度和数据存取速度得到大大提高

- 80486增加了多处理器指令,增强了多重处理系统,片上硬件确保了超高速缓存一致性协议,并支持多级超高速缓存结构。

- 80486具有机内自测试功能,可以广泛地测试片上逻辑电路、超高速缓存和片上分页转换高速缓存,支持硬件测试、Intel软件和扩展的第三者软件。

80486的基本结构

80486CPU的内部结构如图所示,它包括总线接口部件、片内高速缓冲存储器Cache、指令预取、指令译码、控制/保护、整数、浮点运算、分段和分页等功能部件。80486将这些部件集成在一块芯片上,既可以减少主板空间,还可以提高CPU的执行速度。

Pentium系列微处理器

Pentium系列微型计算机的主要特点

- 高集成度,片内集成有310万个晶体管。

- 时钟频率高,从60MHz或66MHz发展到500MHz,700MHz和1500MHz。

- 数据总线带宽增加,内部总线为32位,外部数据总线宽度为64位。

- 内采用分立的指令Cache和数据Cache结构,可无冲突地同时完成指令预取和数据读写。

- 采用RISC型超标量结构。超标量是指微处理器内具有多条指令执行流水线,以增加每个时钟周期内可以执行的指令数,从而使微处理器的运行速度成倍提高。

- 高性能的浮点运算器。Pentium采用全新设计的增强型浮点运算器(FPU),使得它的浮点运算速度比80486DX要快3~5倍

- 双重分离式高速缓存。将指令高速缓存与数据高速缓存分离,各自拥有独立的8KB高速缓存。

- 增强了错误检测与报告功能。内部增强了错误检测与报告功能,特别引进了片功能冗余检测(FRC)。

- 64位数据总线。Pentium为了大幅度提高数据传输速度而使用64位的数据总线。

- 分支指令预测。处理器内部采用了分支预测技术,大大提高了流水线执行效率。

- 常用指令固化及微代码改进。把一些常用的指令改用硬件实现,不再使用微代码操作。

- 系统管理方式。具有实地址方式、保护方式、虚拟8086方式及具有特色的SMM(系统管理方式)。

- 软件向上兼容 80386/80486,可以在MS-DOS,Windows 95,Windows NT,OS/2,UNIX和Solaris等操作系统下运行。

Pentium微处理器的内部结构

Pentium微处理器的主要部件包括总线接口部件、指令高速缓存器、数据高速缓存器、指令预取部件(指令预取缓冲器)与转移目标缓冲器、寄存器组、指令译码部件、具有两条流水线的整数处理部件(U流水线和V流水线)、拥有加乘除运算且具有多用途电路的流水浮点处理部件FPU等。

__EOF__

Recommend

About Joyk

Aggregate valuable and interesting links.

Joyk means Joy of geeK