下一代EUV光刻机,万事俱备?

source link: https://www.36kr.com/p/1761625607829761

Go to the source link to view the article. You can view the picture content, updated content and better typesetting reading experience. If the link is broken, please click the button below to view the snapshot at that time.

光刻机在半导体领域一向是个热门话题,这个能一次又一次突破工艺极限的设备仿佛一个时光机器,连接着芯片的现在和未来。从ASML宣布将推出下一代光刻机开始,人们的目光就从当前最新一代的0.33 NA光刻系统转移到了下一代0.55NA 光刻系统身上。

不知道会不会有人和笔者一样,一边感叹着时间就像是被狗追着一样,跑得飞快,一边又期待着2025年的到来,因为从目前的消息来看,售价4亿美元的下一代光刻机很有可能将在2025年投入使用。

那么,为什么需要High-NA EUV 光刻机?目前下一代光刻机的进展如何?而它又将面临哪些挑战?

为什么是High-NA

众所周知,光刻机的主要作用是将芯片电路图转移到硅片上,而光刻技术正是决定芯片电路大小的关键因素。在芯片制造中,电路越小越好,因为在相同空间中封装的晶体管越多,芯片的速度和能效就越高。

在28nm 及以上的时代,芯片制造的过程应该算是相对简单的,只需要将设计好的芯片图案印在掩膜上,并把掩膜放置在光刻扫描仪中,扫描仪只需要进行单次光刻曝光,就可以把电路图“雕刻”在晶片上,这属于最简单的单一图案化工艺。

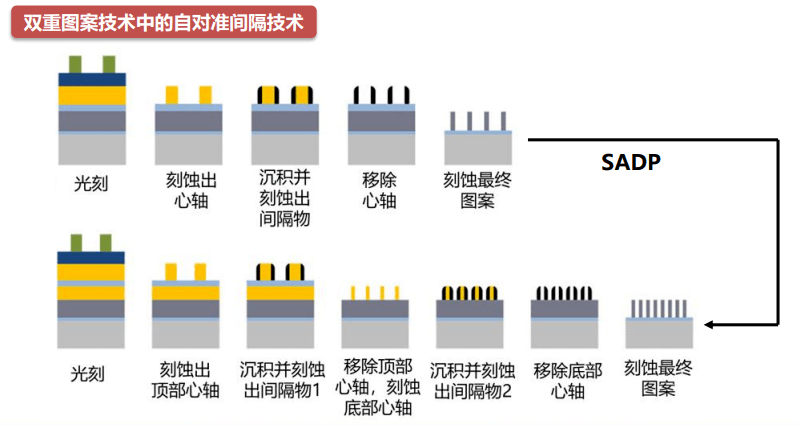

但当芯片制程工艺来到了22nm节点,随着晶体管从平面走向3D,掩膜上的电路图变得密集,使得在晶圆上“雕刻”电路图变得更加困难,大幅提高了芯片制造工艺的难度和成本。为此,芯片制造工艺从上述简单的单一图案化工艺转向多重图案化,芯片电路图不再只被印在一个掩膜上,而是被分割在两个甚至多个掩膜上,分别打印每个掩膜,最终将整套原始绘制的形状成像到晶圆上。为了能把电路图印在晶圆上,芯片制造商使用了各种工艺方案,比如双重图案化或自对准方案,这些工艺技术可以把越来越小的电路印在晶圆上。

图源:方正证券

在EUV光刻机出现之前,技术人员利用193nm的光刻机,也就是我们常说的DUV光刻机,通过把镜头放在水里、相移掩膜、多重曝光的方法,一步步推进芯片技术节点。方正证券曾指出,通过自对准双重图案技术、四重图案化工艺等,理论上是DUV光刻机是可以实现7nm节点工艺制程,但是显然所需的掩膜数量极其多,而且工艺也十分复杂,量产难度很大。

这时候,EUV技术出现了。根据瑞利方程,光刻机所用光源波长越短,越能描绘微细线宽的半导体电路,因此凭借 13.5nm 的极短波长,EUV 光刻被引入以取代 193nm的DUV光刻机。对于芯片金属层M2的间距为 36 nm ~ 38 nm的7 nm/6 nm 节点,以及间距为 30 nm ~ 32 nm的5nm 节点来说,13 nm 分辨率足以让芯片制造工艺再次回到了单一图案化时代。

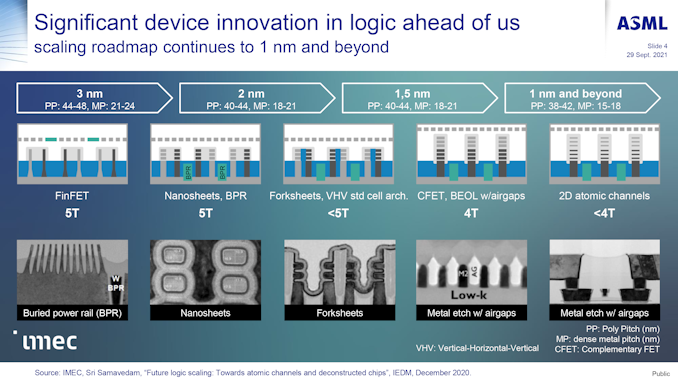

目前,最为先进的5/4nm芯片,以及今年内有望量产的3nm芯片,使用的就是ASML 0.33 NA光刻系统:NXE:3400C或者NXE:3400D。

图源:ASML

但HJL Lithography的Harry Levinson曾指出,金属层M2在 28nm 及以下的间距下,代工厂及其客户有以下选择——双重图案化 EUV、三重图案化EUV 或High-NA。如今3nm还有NXE:3400D来拯救,那2nm甚至1nm节点该怎么办?

对于EUV的多重图案化,专家们分别从技术和成本上给予了否定。Brewer Science高级技术专家 Doug Guerrero 表示:“即使我们将多种图案化技术应用于 EUV,叠加也将非常困难。“Harry Levinson也指出,从经济角度来看,认为双重模式没有意义。

由此看来,为了能让摩尔定律能够继续延续下去,最优解就是High-NA。NA是光学系统的数值孔径,表示光线的入射角度,使用更大的NA透镜可以打印出更小的结构,比如0.55 NA 就能够实现 8nm 分辨率。

一方面,High-NA EUV能够减少晶圆厂的周期时间,因为单次High NA 所需的总处理量将少于多次通过 0.33 NA EUV 的总处理时间。另一方面,也提高了芯片设计的灵活性,某些设计元素只能在单个掩模中实现,而High NA 为这些元素提供了改进的成像窗口。更重要的是,工艺步骤的减少还能提高了芯片的产量。

从这方面来说,High-NA EUV是必然的选择。

当前,进展如何

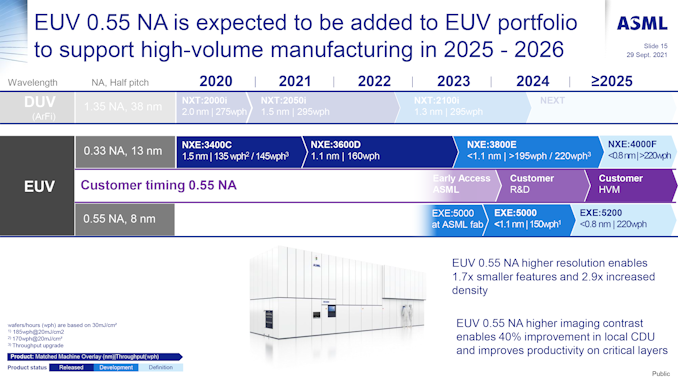

既然ASML 下一代EUV 0.55 NA光刻机的时间表已出,那么现在,它的进展又如何?

据路透社最新消息,ASML 位于荷兰 Veldhoven 镇总部的高管告诉路透社,原型机有望在 2023 年上半年完成。也就是说原型机还有一年就可以完成了。

图源:ASML

此外,ASML 首席执行官 Peter Wennink在4月透露,目前在位于 Veldhoven 的新洁净室中已经开始集成第一个High-NA 系统。今年第一季度收到了多个 EXE:5200 系统的订单,4 月还收到了额外的 EXE:5200 订单。目前,ASML收到了来自三个逻辑厂商和两个存储厂商的 High-NA 订单。

同时,ASML还正在与比利时电子研究中心IMEC建立一个测试实验室,将在其中建造高 NA 系统,连接到涂层和开发轨道,配备计量设备,并建立与高NA工具开发相伴的基础设施——包括变形成像、新掩膜技术、计量、抗蚀剂筛选和薄膜图案化材料开发等,并准备最早在2025 年使用生产模型,在 2026 年实现大批量生产。

当然,光刻机作为一个由来自全球近800家供货商的多个模块和数十万个零件组成的“庞然巨物”,仅靠ASML一家努力是远远不够的,其他和光刻机有关的厂商也已奔赴战场。

在镜头方面,蔡司和ASML将在High-NA光刻机上采用变形镜头,他们通过在垂直于入射平面的方向上保持 4 ×镜头缩小解决了晶圆上最大曝光场尺寸过小问题,从而得到 26 mm × 用于High NA EUV 光刻机 16.5 mm 的视场大小。

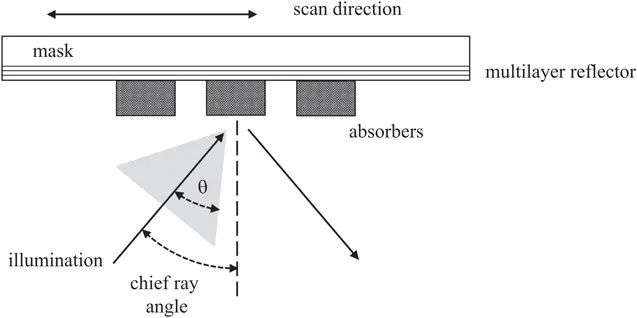

光照下的 EUV 掩模示意图 图源:日本应用物理学杂志

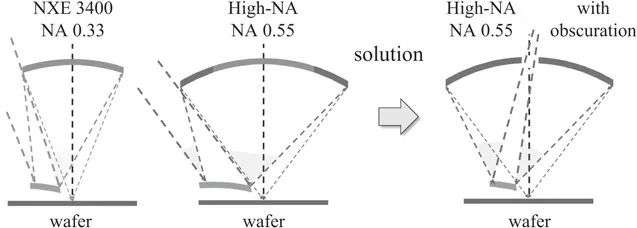

此外,多层反射镜具有高反射率的窄入射角范围对透镜和掩膜都有影响,将当前一代 0.33 NA 镜头的镜头设计概念扩展到 0.55 NA 会导致镜面入射角较大,这是有问题的。因此,蔡司使用一种不同类型的高数值孔径设计,以减少反射镜上的最大入射角,这种新设计的一个基本特征是中央遮蔽,具有中央遮蔽的高性能镜头已被用于其他应用,例如天文学,哈勃太空望远镜就是一个众所周知的例子。

EUV 透镜中最后两个反射镜的图示 图源:日本应用物理学杂志

而日本测试设备制造商Lasertec对于High-NAEUV,正在开发一种具有 1nm x 30nm 灵敏度的用于 EUV 掩膜坯料的光化坯料检测 (ABI) 新系统。USA 总裁Masashi Sunako曾表示“我们的目标是缺陷定位精度为10nm。”

据了解,Lasertec还推出了使用 13.5nm 光源的光化图案掩膜检测 (APMI) 系统,能够定位 EUV 掩模的20nm缺陷。当然,其对于High-NA EUV掩模的 APMI 系统也在开发中,据悉,新的光学器件、探测器和系统设计已经完成,计划用于2023/2024 年。

此外,KLA 和 NuFlare 也在开发多束电子束掩模检测工具。其中,NuFlare 正在开发具有 100 束光束的多光束检测系统,计划于 2023 年推出。NuFlare 的Tadayuki Sugimori 指出,该系统灵敏度为 15nm,每个掩膜检查周期的检查时间为 6 小时。

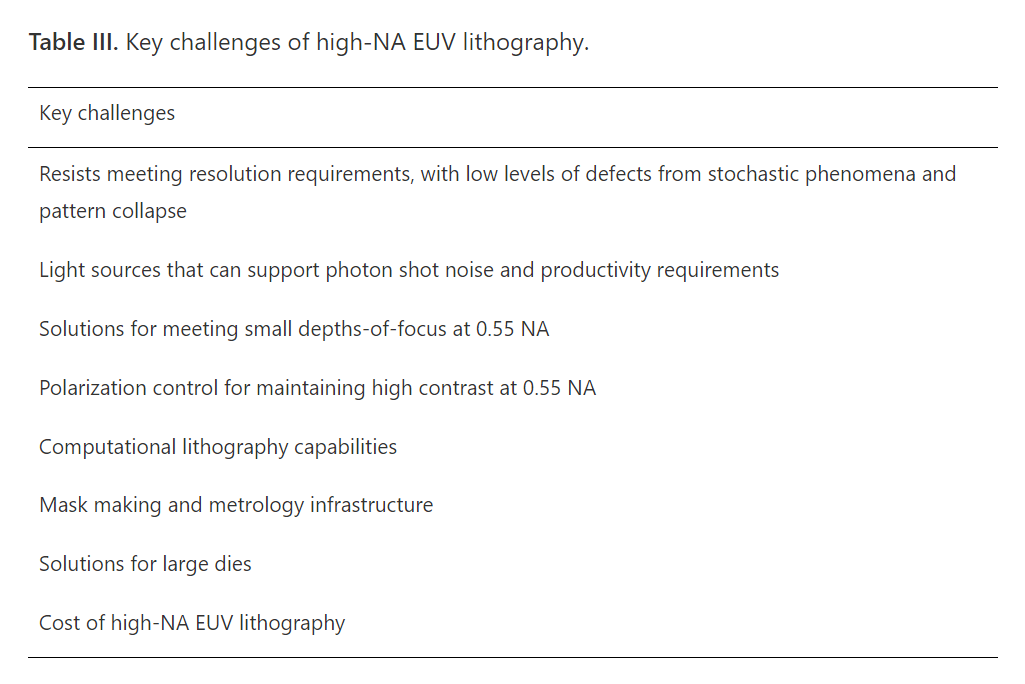

未来,挑战依旧重重

即便厂商们都在努力,但想要制造出High-NA EUV依然有着不小的挑战。近期,在日本应用物理学杂志4月发表的《高数值孔径 EUV 光刻:现状和未来展望》论文列出了High-NA EUV面对的八大挑战,分别是:无法满足分辨率要求,随机现象和图案崩溃可能影响良率;可以支持光子散粒噪声和生产力要求的光源;满足 0.55 NA 小焦深的解决方案;偏振控制,用于在 0.55 NA 下保持高对比度;计算光刻能力;掩膜制造和计量基础设施;大芯片解决方案;High-NA EUV 光刻成本。

图源:日本应用物理学杂志

- 分辨率的要求

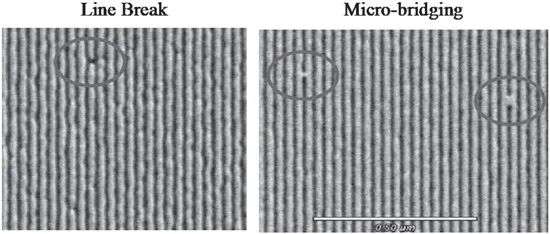

长期以来,光刻胶一直限制着EUV光刻能力,并随着技术的发展,不断减薄,这也使得线条边缘粗糙度 (LER)不断增加。早在ArF 光刻的时候,人们就已经意识到LER的问题,但那时候它对芯片制造影响不大,但随着工艺节点不断微缩,LER就开始影响线宽控制和器件性能。想要降低LER带来的影响,就必须实现低LER。

使用 EUV 光刻图案化的 30 nm 线/空间中随机引起的缺陷示例 图源:日本应用物理学杂志

另一方面,许多不同类型的 EUV 光刻胶都有个共同特征,那就是模糊。除了由电子引起的图像模糊外,在曝光后烘烤过程中,由于光酸扩散,化学放大抗蚀剂也会出现额外的模糊,在某种程度上也会影响良率。

当前,以 10 nm ½ 间距及以下为目标的光刻胶的研发仍在进行中,必须克服目前化学放大型抗蚀剂存在的许多问题,但目前还没有发现具有低LER、低水平的随机性缺陷、无图案塌陷和必要的分辨率,同时避免过高曝光剂量的光刻胶,需要继续研发、改进。

·光源

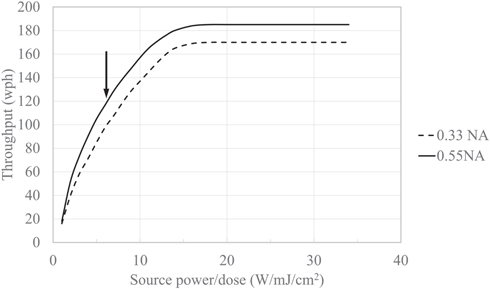

无论是光刻胶还是其他特定材料配方,都存在一个剂量,低于该剂量时光子散粒噪声引起的 LER 和缺陷太大而无法满足技术要求,因此需要有足够高输出功率的光源以避免降低吞吐量和生产率。

ASML 的 EUV 曝光工具的吞吐量作为源功率 (W) 除以曝光剂量 (mJ cm -2 ) 的函数。箭头指示具有 500 W 源和 80 mJ cm -2暴露剂量的工具的点。

图源:日本应用物理学杂志

ASML SanDiego 使用其激光产生的等离子体 (LPP) 光源实现了 400-500 W 的输出,通过将红外激光转换为波段内EUV光的更高效率,提高了脉冲间重复性,增加LPP 光源的输出。此外,人们还把自由电子激光器认为是 LPP 光源的替代品。目前来看,ASML仍在努力实现更高的光输出。

·满足 0.55 NA 小焦深的解决方案

焦深(DOF)一直也属于光学投影光刻的挑战。当NA为0.55 时,DOF明显降低,大约是0.33 NA 的 1/3,因此需要改进聚焦控制来实现高数值孔径 EUV 光刻。在这方面,为了获得良好的成像,光刻胶减薄就非常重要,但当光刻胶薄膜变得非常薄时,又会存在诸如组件偏析之类的现象,降低图案化。

此外,焦点控制不仅仅是光刻技术中的问题,还对晶圆平整度提出了更高的要求,这也对薄膜沉积,尤其是化学机械抛光 (CMP) 提出了严格的要求。

·偏振控制,用于在 0.55 NA 下保持高对比度

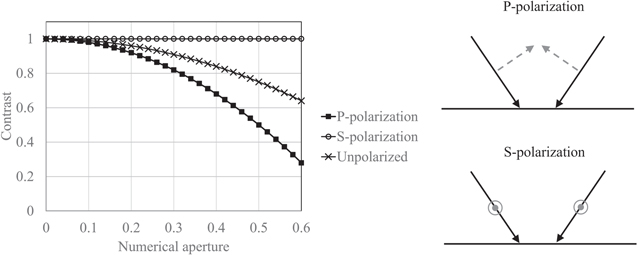

在High-NA下,图像对比度取决于照明的偏振。如下图所示,两个干涉平面波的图像对比度可以在S偏振光的大NA下保持,但随着NA的增加,P偏振和非偏振光的对比度变小。出于这个原因,浸入式光刻机的照明系统提供了偏振控制,并计划在High NA 曝光工具上初始使用的激光产生的等离子体 (LPP) 光源产生非偏振光。当在0.55 NA 处使用非偏振光时图像对比度会明显下降。另一方面,自由电子激光器的发射是偏振的,这为考虑将自由电子激光器 (FEL) 作为High NA EUV 曝光系统的光源提供了额外的动力。

给定数值孔径支持的两个干涉平面波在最大入射角下产生的图像对比。

对于 S 偏振,偏振矢量垂直于入射平面,而对于 P 偏振光,它们位于入射平面内。

图源:日本应用物理学杂志

·计算光刻能力

计算精度需要考虑许多物理现象,同时与高 NA 相关的小焦深增加了对计算解决方案的需求。当前,反向光刻技术 (ILT) 已被证明可用于构建最大化工艺窗口的掩膜版图,并且由于 ILT 的应用而产生的最佳掩膜布局通常呈曲线,让掩膜制造变得更加困难。

而多光束掩模写入器解决了这个问题,不仅让生产具有曲线图案的高质量掩模成为可能,还开始对掩膜上曲线特征的数据格式进行标准化。虽然ILT 和曲线特征并不是High NA EUV 所独有的,但这些功能在High NA EUV 上逐渐成熟,因此有望成为High NA 技术的重要组成部分。

·掩膜制造和计量基础设施

光掩膜是芯片制造的重要组成部分,随着电路图越来越小,与理想掩膜的偏差越来越大,进而影响了最终晶圆的图案。因此需要解决掩膜难题,包括减少掩膜3D 效果、增强对掩膜寿命等。最重要的是,在High NA EUV 光学系统中引入新光掩模类型也给掩膜行业带来额外的复杂性。

当前基于钽的吸收器通常约为 60-70nm 厚,旨在吸收足够量的光,与13.5nm 波长相比,厚度较大,因此以特定入射角(在传统 EUV 光刻中以 6° 为中心)照射掩膜,会扭曲空中图像,最终转移到光刻胶中的光图案,并降低其图像对比度。这些所谓的掩膜 3D 效果还伴随着更多的特征相关变化和对晶圆的最佳聚焦,这对DOF原本就已经降低的High NA EUV 光刻技术提出了额外的挑战。

当然,随着掩膜逐渐变得复杂,对设备的要求也日渐提升。

·大芯片解决方案

当前大芯片十分火热,但却由于尺寸太大无法适应高 NA 曝光工具的 ½ 场。为了能够继续生产具有相似尺寸的芯片,需要采用拼接。换句话说,就是一部分芯片使用一个掩膜进行图案转印,而其余部分通过第二个掩膜曝光进行图案转印。

拼接不是一种新的光刻技术,但需要非常精确实施。此外,由于 EUV 吸收剂不能完全有效地抑制反射光,因此往往通过蚀刻去除掩膜版曝光区域周围的多层反射器,而蚀刻黑色边框会导致局部应力降低,进而影响掩膜特征。

·High-NA EUV 光刻的成本

成本一直是光刻机关注的问题,光刻机价格昂贵不是一天两天了,显然High NA EUV光刻机只会更贵,其成本预计将超过 3 亿美元。前面几代光刻机,其价格的指数增长被吞吐量的提高所抵消,由此可以看出光刻机的吞吐量尤为重要。

因此,如何提高光刻机的吞吐量成为了关键,从这方面来看,提高光源的功率是解决办法之一。一方面,ASML San Diego 已经为 LPP 源实现了 400-500 W 的源功率,并且计划实现更高的功率。另一方面,除了提供偏振光外,自由电子激光器预计具有高功率,这也是考虑将自由电子激光器作为 EUV光刻机光源的另一个原因。

但当光源高于800 W后,High NA EUV 光刻机的吞吐量将接近机械极限,届时又将面临新的难题。

写在最后

总的来说,光刻机向High NA迈进已经成为“续命”摩尔定律的必经之路,在日前举办的的SPIE Advanced Lithography and Patterning上,甚至开始讨论如何转向 0.7 NA EUV。但显然,横跨在大家面前的,仍是不小的挑战。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

本文来自微信公众号 “半导体行业观察”(ID:icbank),作者:龚佳佳,36氪经授权发布。

该文观点仅代表作者本人,36氪平台仅提供信息存储空间服务。

Recommend

About Joyk

Aggregate valuable and interesting links.

Joyk means Joy of geeK