腹背受“敌”的FinFET

source link: https://www.36kr.com/p/1704926982805254

Go to the source link to view the article. You can view the picture content, updated content and better typesetting reading experience. If the link is broken, please click the button below to view the snapshot at that time.

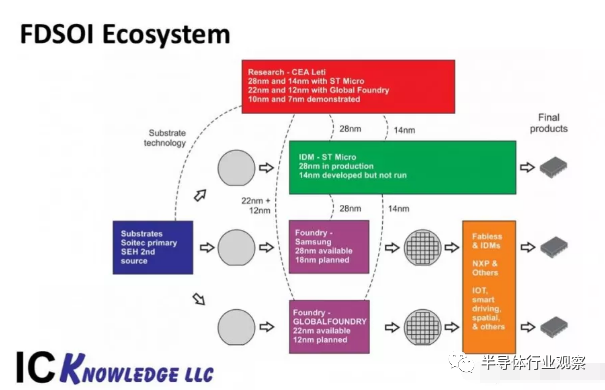

近日,CEA、Soitec、GlobalFoundries和ST宣布了一项新的合作,他们打算共同定义业界下一代 FD-SOI 路线图技术。

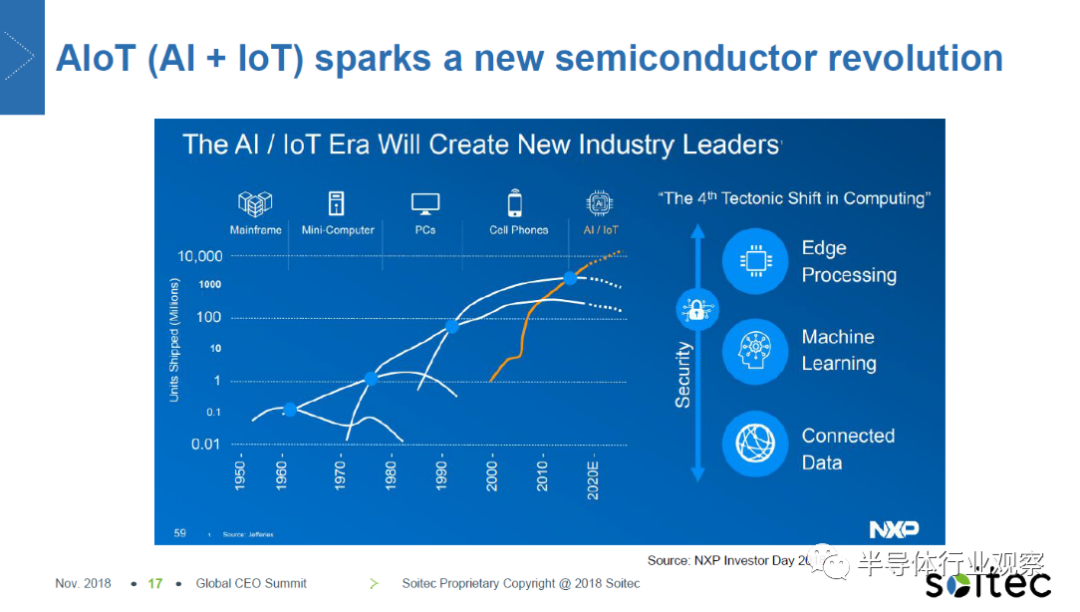

作为本世纪初被开发以应对22nm以后半导体工艺难题的两大制程技术之一,FD-SOI显然从知名度上远远不如FinFET那样耳熟能详,应用广度也欠缺了不止一个维度,但这种独特的工艺在某些方面的优势,又是标准的FinFET工艺所不具备的,特别是在如今庞大的物联网生态中,对芯片差异化的需求有时正需要FD-SOI这种技术独特的优势来实现。

而另一边,长期受益于摩尔定律大放异彩的FinFET仿佛也走到了尽头,如果说三星宣称将在3nm推出其“环绕式栅极(GAA)”技术取代FinFET晶体管技术,FinFET犹可淡定;而到如今,台积电2nm和英特尔5nm制程也将放弃FinFET而转向GAA,就已有一个时代翻篇的迹象了。

三大代工巨头纷纷在下一代先进制程上选择GAA,成熟制程上FD-SOI又在“穷追不舍”,FinFET迎来“前后夹击”。

FinFET的“得意”与“失意”

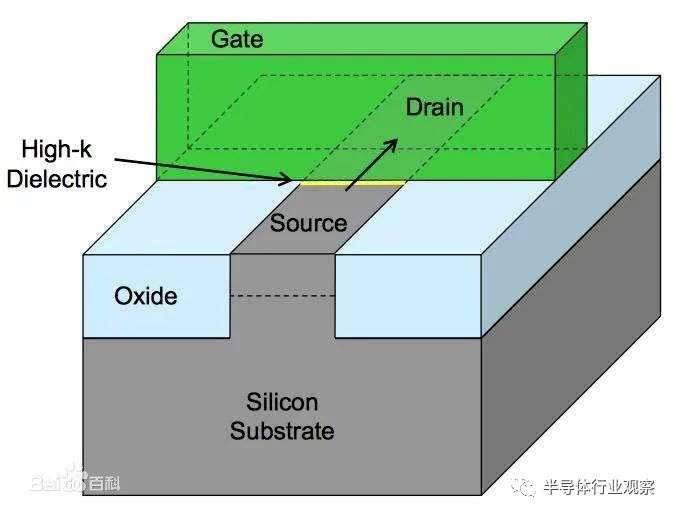

回顾半导体工艺制程发展历程,在过去的很长一段时间里都是平面型晶体管的天下。随着半导体发展趋势,使得相同面积下试图填入更多晶体管的想法逐渐受到重视,因此衍生出微缩整体尺寸的构想,栅极尺寸将是微缩重点。

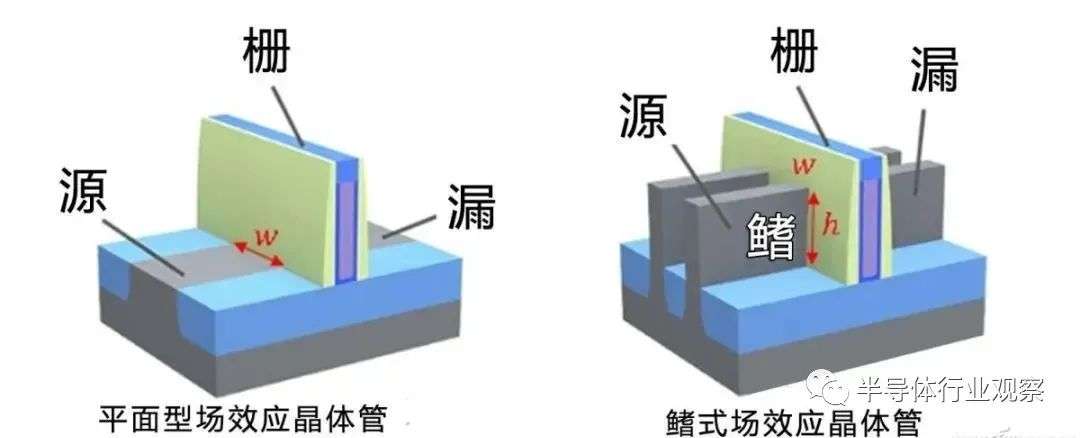

然而平面型晶体管受制于物理结构,它只能在栅极(Gate)的一侧控制电流的接通与断开,而且它的栅极宽度不可能无限制的缩窄。当宽度接近20nm时,栅极对电流的控制能力将出现断崖式下降,业内将其称为“沟道长度变短导致的所谓短沟道效应”,从而出现严重的电流泄露(漏电)现象,最终让芯片的发热和耗电失控。

至此,传统的平面MOSFET结构看似走到了“尽头”。

为了继续延续摩尔定律,胡正明教授于2000年前后提出了两种解决途径:一种是立体型结构的FinFET晶体管(鳍式场效应晶体管),另一种是基于SOI的超薄绝缘层上硅体技术FD-SOI晶体管技术(超薄绝缘层上硅体技术)。

之后两者走出了不同的发展道路。

其中,FinFET工艺先拔头筹,英特尔最早于2011年推出了商业化的FinFET工艺技术,将FinFET技术应用到了自家的22nm制程工艺上,显著提高了性能并降低了功耗,之后台积电、三星等全球各大厂商陆续跟进,采用 FinFET 技术取得了巨大成功,使得FinFET大放异彩,从16/14nm开始,FinFET成为了半导体器件的主流选择,成功地推动了从22nm到5nm等数代半导体工艺的发展,并将扩展到3nm工艺节点,成为全球主流晶圆厂的“不二”之选。

FinFET最大的特色就是将晶体管的结构从平面变立体,对栅极形状进行改制,闸门被设计成类似鱼鳍的叉状3D架构,位于电路的两侧控制电流的接通与断开,大幅度提升了源极和栅极的接触面积,减少栅极宽度的同时降低漏电率,让晶体管空间利用率大大增加。

FinFET工艺技术自2011年商业化以来,体系结构持续进行改进,以提高性能并减小面积。到了5nm节点后,虽然使用了EUV光刻技术,但是基于FinFET结构进行芯片尺寸的缩小变得愈发困难。

而当制程工艺跨过5nm门槛后更是将会出现一系列新的问题。比如,随着栅极宽度的进一步缩小,很难再像过去那样在一个单元内填充多个鳍线,而鳍式场效应晶体管的静电问题也会严重制约晶体管性能的进一步提升。

换句话说,FinFET在5nm时代就已逼近极限,想生产更具能效比的3nm和2nm工艺,需要下一代晶体管技术救场。

随着三星、英特尔两大晶圆代工巨头率先转向GAA工艺,正在预示着在更先进的节点上,FinFET将走向终结。根据国际器件和系统路线图(IRDS)的规划,在2021-2022年以后,最先进工艺制程中的FinFET结构将逐步被GAA结构所取代。

GAA登场,接棒FinFET

随着三星率先“垂范”,以及后续台积电和英特尔的跟进,GAA已俨然成为接棒FinFET的新贵。

GAA全称Gate-All-Around,是一种新型的环绕式栅极晶体管技术,通过使用纳米片设备制造出了MBC FET(多桥通道场效应管),可以显著增强晶体管性能。

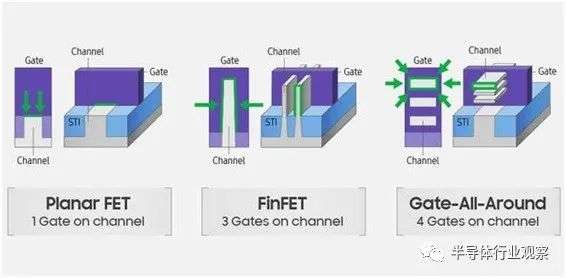

平面硅、FinFET、GAA结构 (图源:中关村在线)

与FinFET的不同之处在于,GAA设计通道的四个面周围有栅极,减少漏电压并改善了对通道的控制,这是缩小工艺节点时的基本步骤。通过使用更高效的晶体管设计,加上更小的节点,将能实现更好的能耗比。

根据三星的说法,与7nm制造工艺相比,3nm GAA技术的逻辑面积效率提高了45%以上,功耗降低了50%,性能提高了约35%。据悉,搭载此项技术的首批3nm三星芯片将于今年上半年实现量产。

GAA标志着代工业务的一个新时代。

虽然GAA取代FinFET已成业内共识,但现阶段影响其量产普及的因素还有不少,复杂的制造流程、良品率、成本难以控制等等仍是阻碍。此外,GAA技术也有几种不同的路线,未来的细节有待进一步验证。而且,转向GAA无疑涉及架构的改变,这将对设备提出不同的要求,据悉一些设备厂商还在开发特殊的刻蚀、薄膜设备在应对。

综合来看,虽然仍有诸多挑战,但GAA技术的推进,将在很大程度上推动半导体工艺特别是先进制程上的发展。

回看FinFET,虽然FinFET无法再继续深耕更先进的工艺节点,但在现有业务布局中仍占有相当份额。然而从FD-SOI行业厂商的动作来看,FinFET这一利基市场似乎也正在被动摇。

对FinFET技术而言,它追求的是绝对高性能,然而前路已然无望。另外,虽然FinFET在与FD-SOI“二选一”的对垒中先声夺人,但伴随着物联网、人工智能、智能驾驶等应用对芯片提出了全新挑战,尤其是FinFET的制造、研发成本越来越高,以及摩尔定律逐渐失速,FinFET虽到7nm及5nm犹能高歌猛进,但工艺历史的流向或将再次“转向”。

FD-SOI,走出FinFET阴影

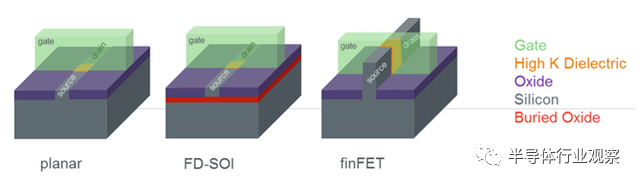

FD-SOI元件技术主要源于一种水平式晶体管结构,透过SOI晶圆方式将最上层Si层借由制程、设计以满足所需功能,并作为元件导通层之用;而中间SiO2层,凭借于高阻值之材料特性,隔绝晶体管间不必要的寄生电容,提高元件工作效率,因此在这样的制程条件下,FD-SOI可透过传统Si芯片的机台进行加工,降低开发所需的设备成本。

FD-SOI与FinFET最大的不同之处在于,FinFET工艺注重晶体管的优化设计,而FD-SOI则注重芯片底衬的设计。从架构设计上看,FD-SOI可以在无需全面改造设备结构、完整性和生产流程的前提下实现摩尔定律下的芯片面积微缩、能耗节省、性能提升及功能拓展。

平面硅、FD-SOI、FinFET结构 (图源:Semiconductor)

多年前与FinFET竞争之时,胡正明教授研究小组认为要让FD-SOI正常工作,绝缘层上硅膜的厚度应限制在栅长的四分之一左右。对25nm栅长的晶体管而言,FD-SOI的硅膜厚度应被控制在5nm左右。限于当时的技术水平,要想制造出如此薄的硅膜实在太过困难,于是产业界开足马力研发FinFET技术。

另一方面,FD-SOI工艺的应用也存在难点,即其衬底价格较为昂贵,也因此限制了FD-SOI的市场拓展,并且越往上走的尺寸越难以做小,后续或难以为继。

因此,在与FinFET的较量中,FD-SOI失去了占领市场的黄金时间窗口,多年来一直活在FinFET的阴影中。

回顾FD-SOI的发展,IBM、三星、格芯、ST、CEA等企业在过去的几十年,一直没有放弃FD-SOI市场化的尝试,除了不断将FD-SOI技术向更先进制程推进以外,还通过提高SOI晶圆产能并降低成本,进一步推动了FD-SOI技术商业化。

总体上,早期的FD-SOI技术处于初期探索阶段,尽管取得了一定的关键技术突破,但始终没有出现具有市场竞争力的产品。CEA公司也曾表示,在FD-SOI上学到的教训之一就是应该从一开始就建立生态。

20多年来,CEA一直是生态系统中FD-SOI技术的先驱。CEA还与ST、Soitec和GlobalFoundries有着长期的深入研发合作历史,并且一直非常积极地参与由欧盟委员会和成员国领导的旨在建立一个完整的FD-SOI生态系统的计划,从材料供应商、设计再到EDA工具。

图源:techweb

在 FD-SOI衬底供应 上,最近几年,正是由于FD-SOI衬底材料取得了突破性进展,特别是超薄BOX(20nm量级)及超薄顶硅(10nm量级)的衬底投入应用,使得纳米级FD-SOI CMOS迅速发展。Soitec是最早实现FD-SOI衬底片成熟量产的公司,也是目前FD-SOI衬底的主要供应商,其300mm晶圆厂能够支持65nm、28nm、22nm及更为先进的节点上大规模采用FD-SOI技术。

主要 FD-SOI代工厂商 中,IBM、意法半导体、格芯、三星等公司,都在提供FD-SOI代工服务,国内中芯国际、华虹集团旗下华力微也在开始尝试FD-SOI工艺。其中,格芯是研发FD-SOI技术最领先的厂商,推出的12nm和22nm FD-SOI工艺技术12/22FDX是目前市面上最先进的FD-SOI制造工艺,随着上下游加入的厂商越来越多,有望逐渐形成完整FD-SOI生态,填补FinFET未能满足的市场技术需求。

据2021年3月数据披露,格芯的22FDX解决方案已经实现了45亿美元的设计营收,向全球客户交付了超过3.5亿枚芯片。

在 FD-SOI设计服务环节 ,目前,众多EDA和IP公司正积极参与FD-SOI的相关研发。芯原股份从2013年就与ST在FD-SOI上展开合作,后续相继与三星、GF等代工厂进行合作,如今能够在28nm和22nm提供IP平台和设计服务,推出了USB 3.0 PHY、混合信号IP等;Cadence和Synopsys也已有经过验证的FD-SOI IP;芯片设计企业联发科、瑞芯微等也已经采用FD-SOI工艺进行布局。

在 FD-SOI产品层面 ,采用28nm FD-SOI制程的产品已涉及应用处理器、GPS、SoC、RF、存储器、AI芯片等,应用于IT网络、消费电子、汽车电子、物联网甚至AI等领域。

能看到,经过多年的打磨,FD-SOI产业生态在逐步壮大,逐渐在全球逐渐打造出完整的产业链,覆盖应用、IC设计、代工、封测、材料等各个环节,具备了一定的产业基础。

随着摩尔定律的放缓,当前业界开始重新将目光移向FD-SOI,凭借FD-SOI在成本和低功耗性能方面的优秀表现,为设计人员和客户系统提供了巨大的优势,包括更低的功耗以及更容易集成附加功能,颇受物联网、汽车电子、网络基础设施和移动应用领域的关注。

在消费电子市场,谷歌最新推出的5G Pixel 6手机中的芯片采用了三星的FDS28(28nm FD-SOI)工艺,其中的FD-SOI衬底来自法国Soitec公司。谷歌此次采用FD-SOI方案,首创性地将FD-SOI引入手机市场,替代了高通的bulk CMOS解决方案,此举为智能手机的设计开创了更多可能。这也或将进一步推动FD-SOI在5G毫米波的发展,未来有望获得更多领域的青睐。

汽车领域,例如Mobileye Eye Q4的视觉处理器就是在28nm的FD-SOI上面实现的;Arbe Robotics公司的4D成像雷达是基于22nm的FD-SOI器件实现;意法半导体的域控制器MCU、恩智浦用于信息娱乐的应用处理器等都采用了FD-SOI技术,大大提升了系统的可靠性和性能。

另一方面,目前用得起FinFET工艺的客户屈指可数。FinFET的工艺制造过程较为复杂,作为先进工艺的成本也较为昂贵。

通过台积电FinFET各节点工艺的命名就可见,不是HP(高性能)就是LP(低功耗),这也说明只有追求更高运算效能,还要求更低的运行功耗的特殊芯片,才采用FinFET工艺。

据Gartner统计,设计28nm芯片的成本约为3000万美元,而16nm或14nm芯片的平均成本约为8000万美元,7nm芯片则达到2.71亿美元。对于业内大多数厂商来说,他们更愿意将资本投入在还有较长生命周期的28nm制程中。

而FD-SOI则在成本和性价比方面更有优势。格芯曾公布数据显示,FD-SOI工艺的光刻层比FinFET工艺少了将近50%,抵消了其衬底成本高过FinFET的部分,16nm或14nm芯片的平均成本降低20%。

FD-SOI虽有成本优势,不过因其仍属于平面工艺,尺寸难以做小,目前来看,在到达12nm之后,将难以再进行缩小。

芯原股份董事长戴伟民曾表示,未来IoT与AI时代需用FinFET和FD-SOI两条腿走路。FinFET更多用于12nm以下高性能的数字芯片领域,FD-SOI则凭高集成、低功耗和低成本等特性,发挥在低功耗、射频集成的优势。

文章开头提到,多家厂商正在合作定义下一代 FD-SOI 路线图技术,加速向先进制程推进。技术研究中心CEA认为,FD-SOI制程可以扩展到10nm以下,这一突破或将给FD-SOI市场带来新的拓展。

FD-SOI的国产机遇

对于在FinFET技术发展上明显受到外部遏制的国内产业而言,FD-SOI同样是一条可能“换道追赶”的技术路径。

为了实现本土半导体的弯道超车,中国从10年前就开始关注和布局FD-SOI技术,目前中国FD-SOI产业链布局已经初见端倪。

在02专项总师叶甜春的带领下,国内已经形成广东大湾区集成电路与系统应用研究院为代表的FD-SOI先进工艺研发力量。叶甜春强调:“现在FinFET往下走已经遇到大量的技术壁垒,FD-SOI开始显现出优点,除了它的性能优势之外,在制造上,它的要求低于FinFET,对于中国已有的产业链装备材料也非常适合。再加上未来中国蓬勃发展的市场,未来我们能不能打造一个新的生态来做这件事情。”

据了解,自2019年以来,已经在面向1X纳米FD-SOI关键技术、光电异质集成、计算光刻等先导性技术研发上取得一系列成果,随着先导成果的积累,在前不久刚刚公布的《广州市半导体与集成电路产业发展行动计划(2022-2024年)》中,已经出现了FD-SOI产业化的具体部署:“建设先进SOI(绝缘体上硅)工艺生产线,力争引进张江国家实验室,重点开展12英寸先进SOI工艺研发,推动与现有制造产线整合,建设FD-SOI(全耗尽绝缘体上硅)工艺研发线、RF-SOI(射频绝缘体上硅)工艺生产线。”

总体而言,随着近期《欧洲芯片法案》、英特尔新厂落地德国等一系列动作,欧盟也已正式加入全球主要国家半导体产业政策的“竞赛”之中,在这样的争竞态势下,中国半导体产业所面临的挑战无疑将进一步加大,如何在激烈的竞争中闯出一条新路,FD-SOI不免被投上了几许目光。

写在最后

在FinFET市场,台积电一支独秀,三星、英特尔奋力追赶;而几乎同一时期诞生的FD-SOI,仍在方块之地寻找破壁之法。当下节点,消费电子市场进入饱和期,汽车电子、物联网时代到来,为FD-SOI扩大市场带来了机会;GAA则已箭在弦上,由摩尔定律引领着三星、英特尔、台积电进入新的赛道继续厮杀。

未来,FinFET、FD-SOI、GAA这彼此胶着的“三国杀”又会呈现怎样的此消彼长?

GAA的战役即将硝烟四起,FD-SOI生态需要一次真正的变革,FinFET在腹背受敌中,思考未来的路...

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

本文来自微信公众号 “半导体行业观察”(ID:icbank),作者:L晨光,36氪经授权发布。

该文观点仅代表作者本人,36氪平台仅提供信息存储空间服务。

Recommend

About Joyk

Aggregate valuable and interesting links.

Joyk means Joy of geeK