初窥 SDRAM

source link: https://blog.strongwong.top//posts/%E5%88%9D%E7%AA%A5-SDRAM.html

Go to the source link to view the article. You can view the picture content, updated content and better typesetting reading experience. If the link is broken, please click the button below to view the snapshot at that time.

初窥 SDRAM

上次挖的坑现在来填,在我们把 SDRAM 控制器接进 AHB 总线之前,我们先来设计一个 SDRAM 控制器。

引用知乎上看见的一段话:

在做这个 SDRAM 控制器之前,博主有一个疑问,对于学生来说,是否有必要学习用纯 Verilog 写一个 SDRAM 控制器?因为目前广告厂(X)和牙膏厂(A)都有了 DDR IP Core,而 SDRAM 的控制 IP 更是漫天飞舞,对于要实现一个应用可以直接调用 IP Core,只需要对其接口操作即可。对于开发者来说,与其费时费力用 Verilog 去写一个性能差而且老的 SDRAM 控制器,还不如直接调用官方经过打磨的更为先进 IP Core。所以博主特地来号称平均学历 211,平均月薪 7、8 万的知(bi)乎提出了这个问题,得到的解答博主总结大致如下。

对于学生这个身份来说,应该是要以学习为主要目的,虽然说目前企业为了加快项目进度会直接使用 IP Core,但是我们以学为本的初衷不应该为了避过难点而直接不去尝试,就比如我们刚开始学 Verilog 的时候肯定都会写过分频器,那么为什么不直接去学更简单精度更高 PLL IP Core 呢?从一个新手逐渐成长成一个老手都是由简单到复杂,由基础到提升,这是一个必经的过程。这也就是很多高校还是会开设汇编语言编写单片机的课程,学 FPGA 全用 IP Core 和学单片机全用库函数是一个道理。这是其一。

第二,写一个 SDRAM 控制器还是可以锻炼一些典型的技能。

- 看官方文档

- 根据时序图设计 SDRAM 逻辑,使用状态机

- 配合仿真模型写测试仿真

- 调试,提高频率,让你的 SDRAM 跑的更快

- 研究时序约束

这一套做下来,你就可以提高一个层次了,经历过和没经历过是有质的区别。其实博主在提问的时候心中早已有了答案,只是还没有足够的信念去完成这个事情,当时看到很多业界前辈都支持去写的时候,博主心里也是比较开心的。之前博主已经学一些 SDRAM 的基础知识,只是当时水平还不够,没有坚持下去,心里一直不甘。趁着最近两个月之内没有什么事情要忙,所以决定要再次死磕 SDRAM。

SDRAM 基本介绍

关于 SDRAM 的基本概念,在这再引用《终极内存指南》这篇文章中的一段话:

SDRAM(Synchronous Dynamic Random Access Memory),同步动态随机存储器。同步是指 Memory 工作需要同步时钟,内部的命令的发送与数据的传输都以它为基准;动态是指存储阵列需要不断刷新来保证存储的数据不丢失,因为 SDRAM 中存储数据是通过电容来工作的,大家知道电容在自然放置状态是会有放电的,如果电放完了,也就意味着 SDRAM 中的数据丢失了,所以 SDRAM 需要在电容的电量放完之前进行刷新;随机是指数据不是线性依次存储,而是自由指定地址进行数据的读写。

下面再简单看一下 SDRAM 的内部结构。

对于 SDRAM 的内容结构,就如同 Excel 的表格(如下图所示),即一个单元格就是一个存储地址。要确定具体的存储位置,只需要知道行地址(row-address )和列地址(column address )即可。

一个常见的 SDRAM 中的一个 BANK 就有如上图所示的 13 行 9 列,通常一个 SDRAM 中有 4 个 BANK,那么 SDRAM(DDR 类似)的计算公式就是:

SDRAM(DDR容量) = 2^(row-address) × 2^(column-address) × 2^(bank-address) × datawidth

= 2^(row-address) × 2^(column-address) × bank数 × datawidth

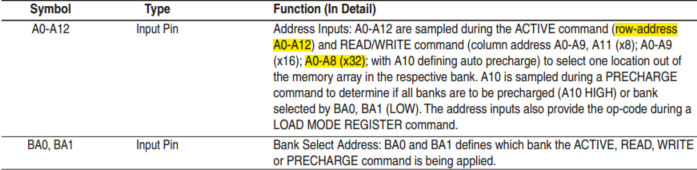

以 DE10-LITE 开发板板载的 SDRAM-IS42S16320D-7TL 为例,标称为 64MB。根据芯片手册(如下图所示)我们可以看见其行地址宽度为 13,列地址宽度为 9(此时数据位宽为 32),则根据公式我们可以算出其容量确实为 64MB

2^13 × 2^9 × 4 × 32 = 536870912 b

⇒ 536870912 b ÷ 1024 = 524288 kb

⇒ 524288 kb ÷ 1024 = 512 Mb

⇒ 512 Mb ÷ 8 = 64 MB

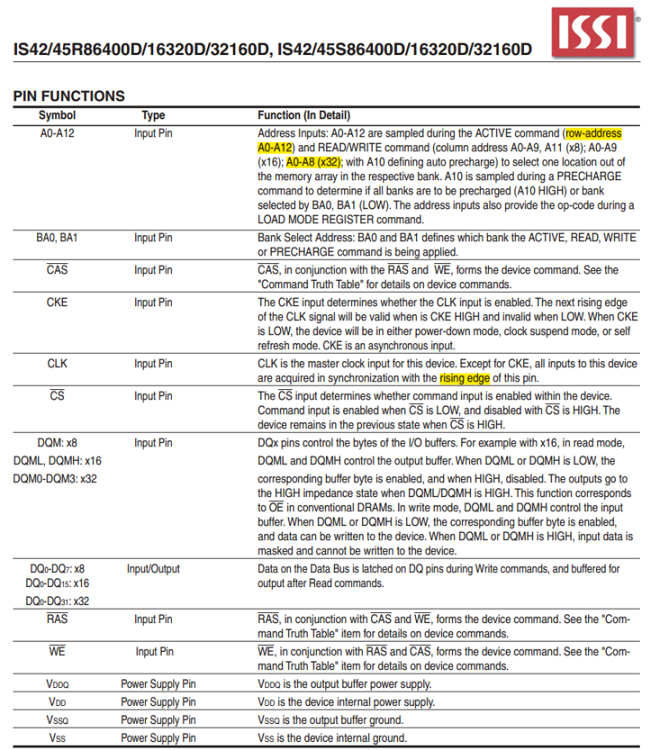

SDRAM 芯片介绍

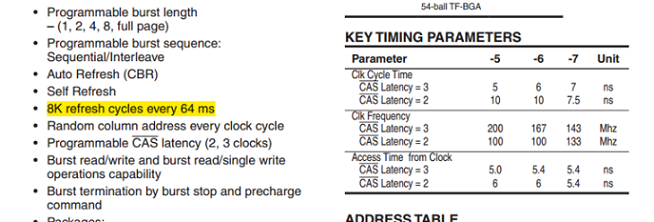

既然都打开了芯片手册(IS42S16320D-7TL),那就不要关上了,那我们再来看看芯片手册中的那些重要参数。

首先我们在第一页就可以看到它的刷新周期是 64ms(这个重要参数将在后面进行具体介绍)

在上文中我们已经提到了该芯片的行地址和列地址,我们需要注意的是其行列地址是复用的,其他相关引脚的功能描述都有介绍。

SDRAM 的初始化及寄存器的配置

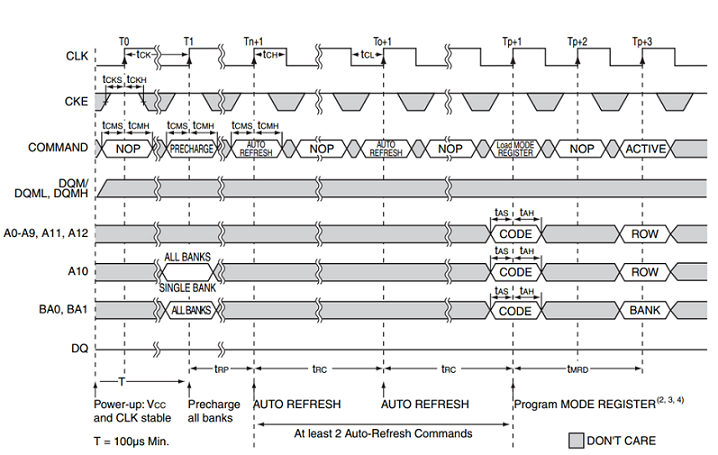

SDRAM 初始化时序图如图所示,首先上电后,电源 Vcc 及 CLK 稳定时间至少 100us,然后对所有 BANK 进行预充电(precharge),经过 tRP 后给 auto refresh 命令,再经过 tRC 后再次 auto refresh 命令,再进过 tRC 后进行模式寄存器的配置。

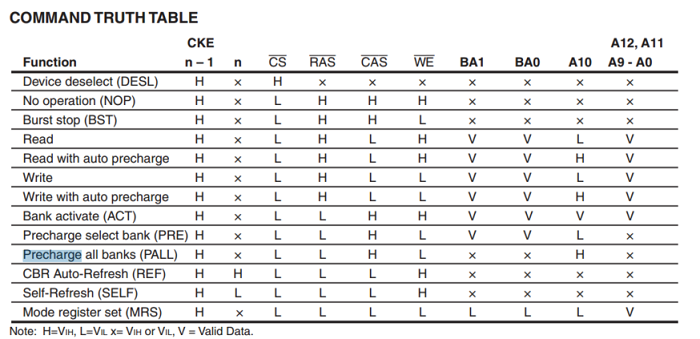

那么以上命令是如何实现的呢,当时就是给与相应管脚的高低电平控制,由此实现,那么这就回到了我们数电的功能真值表(在之前我们就有提到过,数字 IC 终归是数字电路,不要把它搞成了编程项目),我们将下图的真值表以使用顺序总结为表格形式,方便接下来的 RTL 表述。

CMD CS RAS CAS WE

Precharge 0 0 1 0

Auto-Refresh 0 0 0 1

Nop 0 1 1 1

Mode 0 0 0 0

在了解到命令描述后我们还需要注意时间的间隔,在时序图中只告知了我们 T = 100us,而其余的 tRP,tRC,tMRD 均未告诉我们,这是因为通常一个芯片手册中有多种型号的芯片,因此我们需要去查看 AC characteristic 表格,根据芯片型号去确定时间。我们的板载芯片型号为 IS42S16320D-7TL,因此我们选择 -7 对应的时间,则 tRP = 15ns,tRC = 60ns,tMRD = 14ns

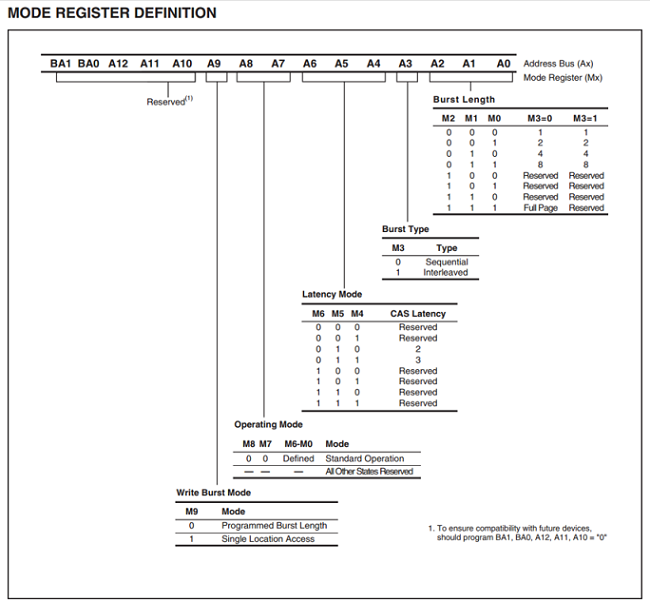

接下来我们就要进入到模式配置,模式配置的配置说明如下图所示:

A0-A2 为突发长度控制,即表示单次读或者写的时候的数据『长度』,本次突发长度参数我们设为 010。A3 突发模式通常设为 0。A4-A6 为潜伏期控制,专门针对读命令时,当给出读命令后,若有设置 CAS latency 则会延迟相应的周期数后给出数据,本次潜伏期参数我们设为 011,A9 突发模式通常设为 0。则最终我们初始化设置参数为 13’b0_0000_0011_0010

至此,我们便可以开始着手设计我们的初始化模块了,首先时序图上 T = 100us Min,则我们取 200us = 200,000ns 在不经过 PLL 的前提下,DE10LITE 开发板默认提供的时钟频率为 50MHz,则一个周期为 20ns,因此 T 延时可以取 10,000clk。延时后我们执行 precharge 命令。之后执行 tRP = 15ns Min,我们的 tRP 延迟就可以取 1clk(至少满足 15ns 的最低要求),然后执行 auto refresh 命令,tRC = 60ns Min 则延迟可取为 4clk,然后再次执行 auto refresh 命令,在这期间一共 9 个 clk。具体的设计可以首先设计一个 200us 的不自清零的计数器;设计一个对应的 200us 计数器标志位;针对 tRP 和 tRC 设计一个计数器,分别实现监测计数到对应的周期发出对应的命令;命令寄存器用来存放对应的命令;最后完成初始化操作后给一个初始化完成的标志位信号。

下面是具体实现的描述语言:

仿真模型(见附件)一共有两个分别是镁光官方仿真模型以及国内大神基于镁光模型进行修改后便于调试的版本,使用任意一版均可。这里我采用的是 sdram_model.v

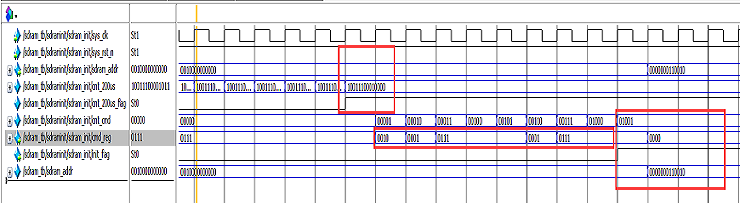

我们可以看到基于 sdram_model.v 运行了 201us 个周期后,modelsim 上打印信息显示我们初始化的操作是正确的。

仿真波形如图所示:

我们依芯片手册成功实现了 sdram 的上电初始化,接下来我们将继续进行后续的操作,我们将尽快更新~

SDRAM 仿真模型文件:点击下载,提取码:yihx

By Ricky

Recommend

About Joyk

Aggregate valuable and interesting links.

Joyk means Joy of geeK