Cadence发布PCIe 6.0 IP测试芯片设计套件,采用台积电5nm工艺制造

source link: https://www.expreview.com/80967.html

Go to the source link to view the article. You can view the picture content, updated content and better typesetting reading experience. If the link is broken, please click the button below to view the snapshot at that time.

Cadence发布PCIe 6.0 IP测试芯片设计套件,采用台积电5nm工艺制造

吕嘉俭发布于 2021-11-5 15:55

本文约 560 字,需 1 分钟阅读

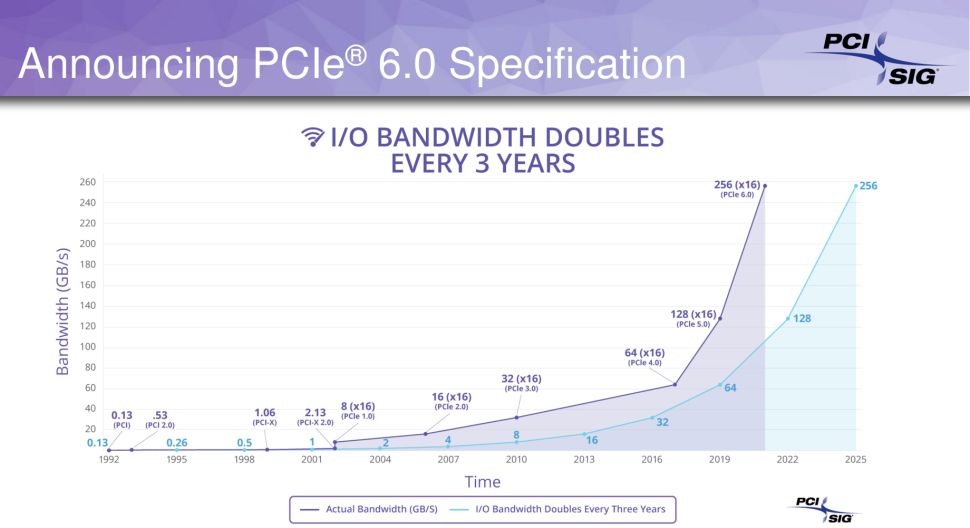

大概在一个月前,PCI-SIG宣布PCIe 6.0已经到了0.9版本,相当于最终草案阶段。目前PCI-SIG成员正在对技术进行内部审查,以确保其知识产权和专利。除非出现重大问题,否则不允许进行任何功能上的修改,相关企业也可以开始在产品中采用PCIe 6.0。

近日,Cadence(楷登电子)宣布推出PCIe 6.0 IP测试芯片设计套件,让芯片开发人员能够在其设计中实现对PCIe 6.0的支持并进行测试,其支持Cadence的智能系统设计战略(Intelligent System Design),实现了SoC的卓越设计。据Cadence介绍,早期的开发人员已开始探索新一代的PCIe 6.0规范,利用Cadence和台积电(TSMC)的技术,或许会在2022年-2023年加入到芯片设计中。

这款面向PCIe 6.0 IP测试芯片设计套件包括基于DSP的高性能PHY和功能丰富的配套控制器,为为超大规模计算和5G通信的新一代应用提供优化的性能和吞吐量。在今年7月份,Cadence的PCIe 6.0子系统测试芯片在台积电N5制程节点上完成流片,其集成了第二代功耗、性能和面积(PPA)优化的PCIe 6.0 PHY与PCIe 6.0控制器。

在PCIe 6.0规范中,数据传输速率从PCIe 5.0的32 GT/s和PCIe 4.0的16 GT/s提高到每引脚64 GT/s,PCIe 6.0 ×16通道单向理论数据传输速度达到了128 GB/s(双向256 GB/s)。为了提高数据传输速率和带宽,新接口采用了四级脉冲振幅调制(PAM4)信令,这种信令也被用于像InfiniBand这种高端网络技术以及GDDR6X内存等地方。此外,PCIe 6.0还采用了低延迟前向纠错(FEC),以确保高效率运行。

Recommend

About Joyk

Aggregate valuable and interesting links.

Joyk means Joy of geeK